MAX32660 User Guide

Maxim Integrated Page 44 of 195

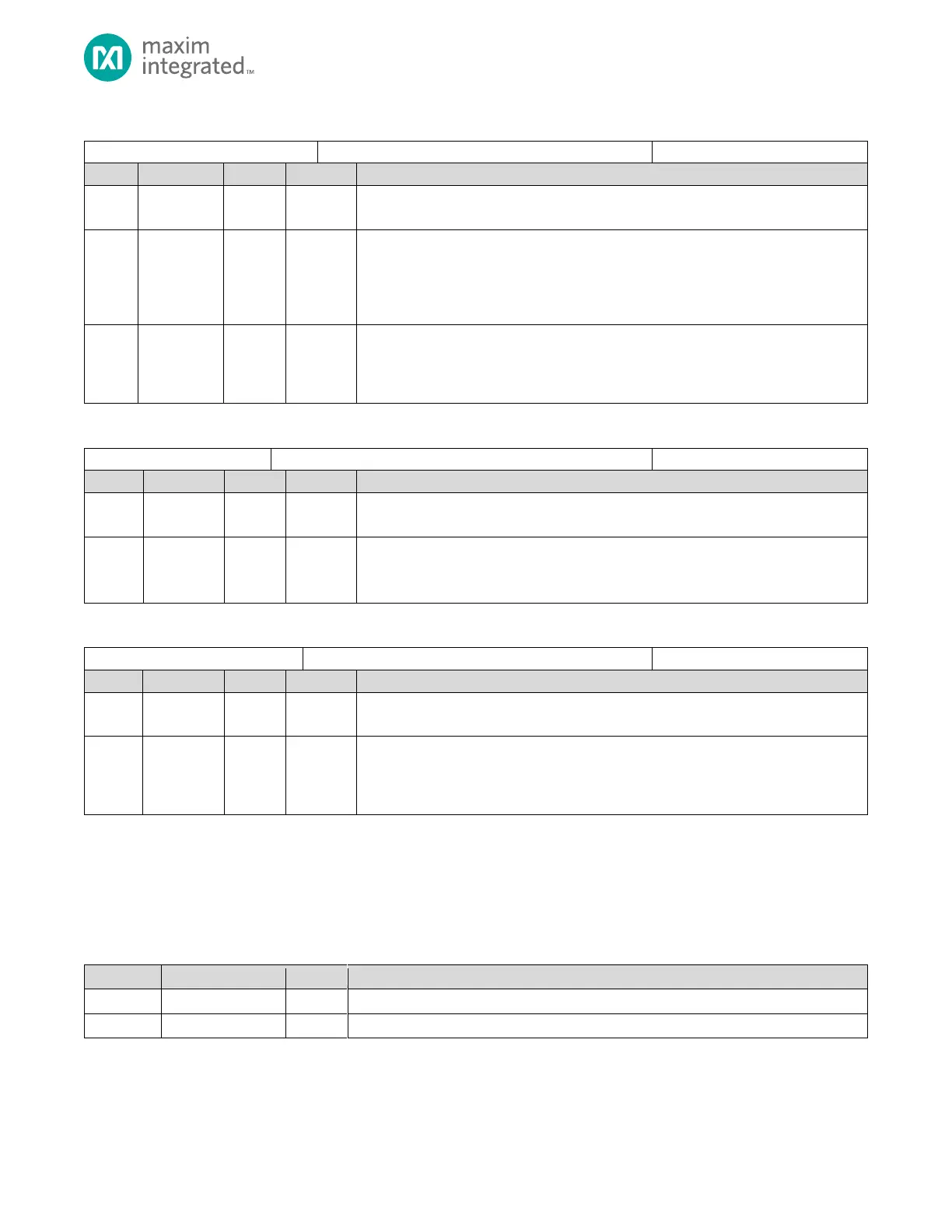

Table 4-23: Event Enable Register

Reserved for Future Use

Do not modify this field.

RX Event Enabled

Set this field to 1 to enable generation of an RXEV event to wake the CPU from a Wait

for Event (WFE) sleep state.

0: RX Event is disable.

1: RX Event is enabled.

DMA CTZ Event Wake-Up Enable

When set, when a DMA block transfer is completed and the DMA counter

DMAn_CNT.cnt = 0, a CTZ DMA event occurs which generates an RXEV to wake-up the

device from a low power mode entered with a WFE instruction.

Table 4-24: Revision Register

Reserved for Future Use

Do not modify this field.

Maxim Integrated Chip Revision

This field reads the chip revision id (A1), ascii encoded.

Table 4-25: System Status Interrupt Enable Register

System Status Interrupt Enable

Reserved for Future Use

Do not modify this field.

Arm ICE Unlocked Interrupt Enable

Set this bit to enable a PWRSEQ IRQ if the Arm ICE is unlocked.

0: Interrupt disabled

1: Interrupt enabled

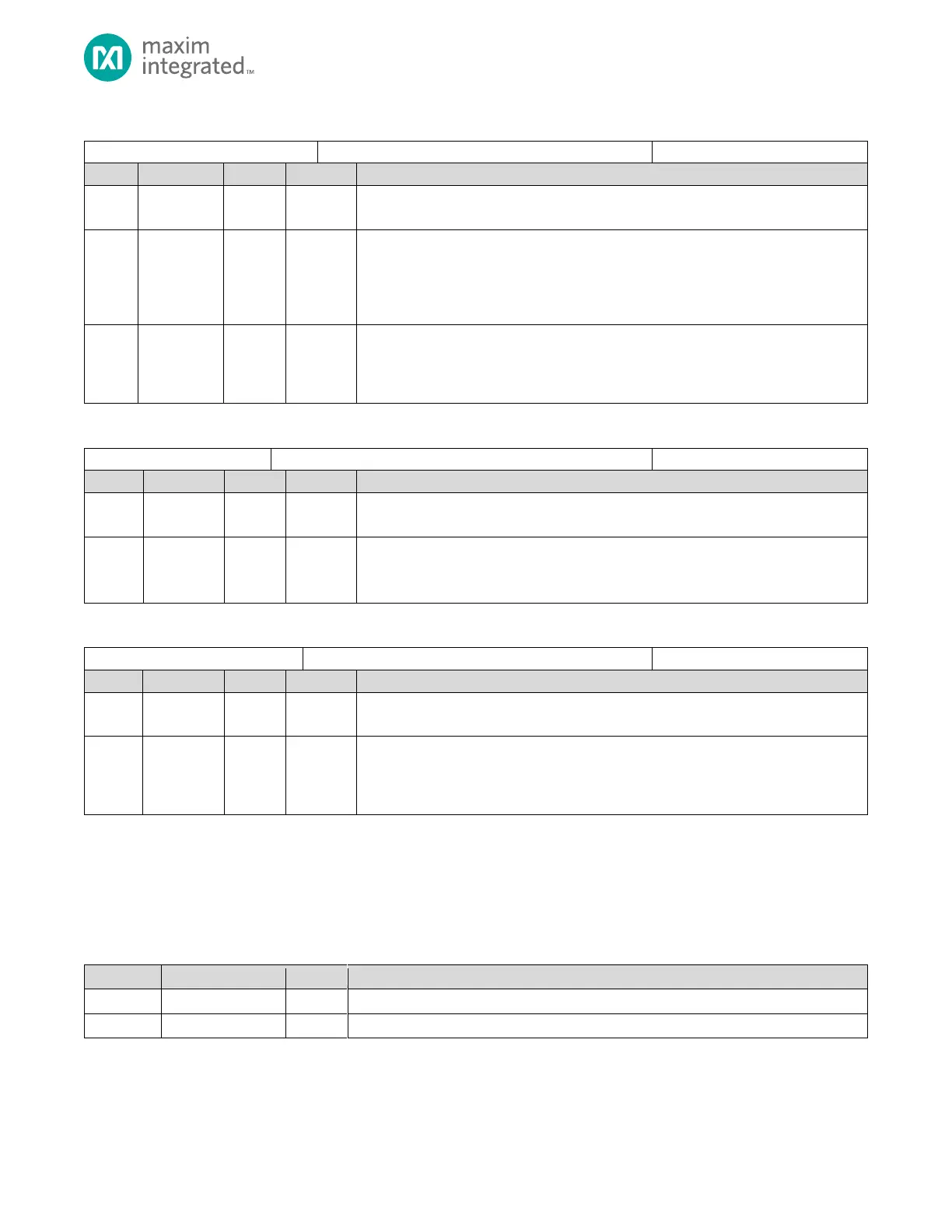

4.12 System Initialization Registers

The SIR base peripheral address is 0x4000 0400. Refer to Table 3-1: APB Peripheral Base Address Map for the addresses of

all APB mapped peripherals.

Table 4-26: System Initialization Registers, Offsets and Descriptions

System Initialization Status Register

System Initialization Address Error Register

Loading...

Loading...