MAX32660 User Guide

Maxim Integrated Page 126 of 195

11 Watchdog Timer (WDT)

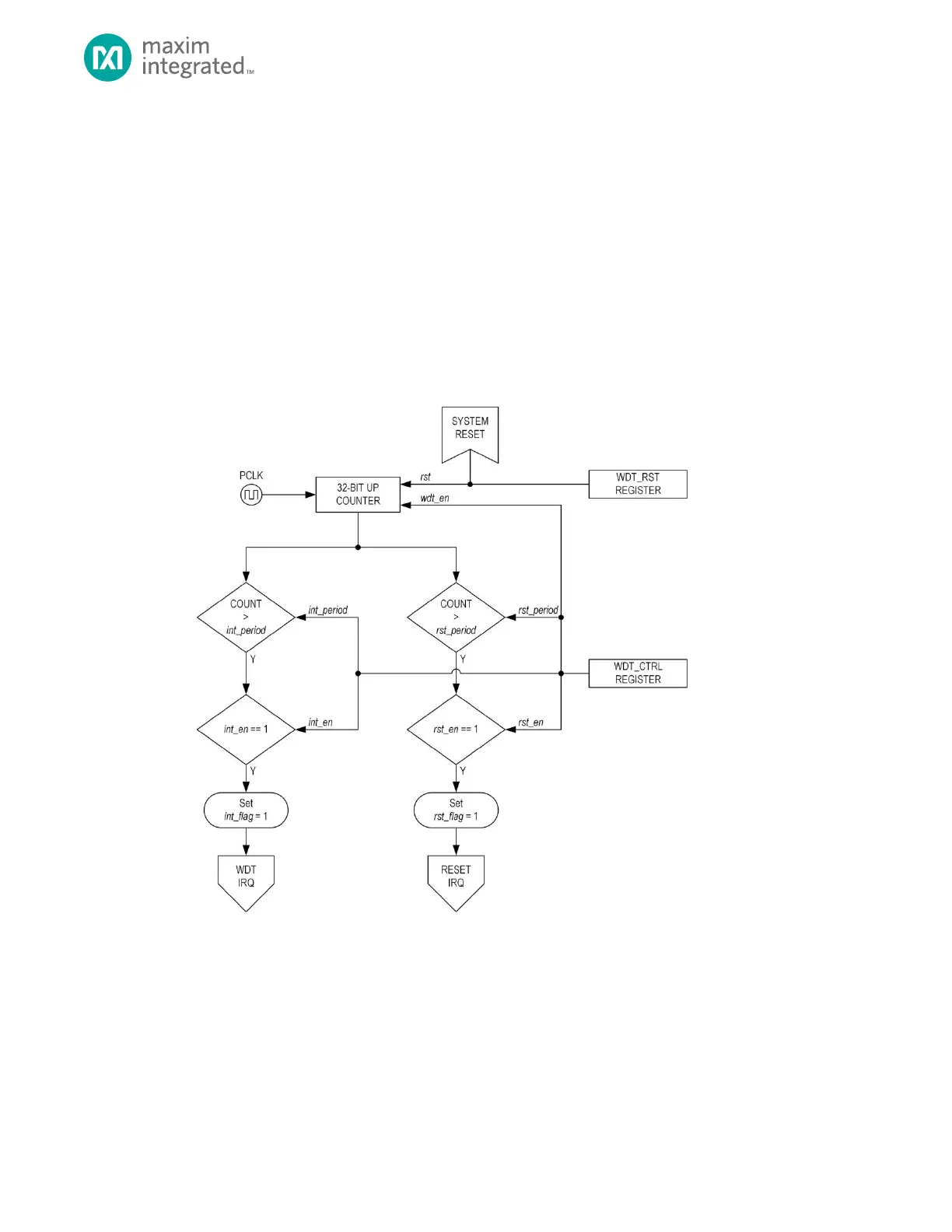

The watchdog timer protects against corrupt or unreliable software, power faults, and other system-level problems, which

may place the microcontroller into an improper operating state. When the application is executing properly, application

software periodically resets the watchdog counter. If the watchdog timer interrupt is enabled and the software does not

reset the counter within the interrupt time period (WDT0_CTRL.int_period), the watchdog timer generates a watchdog

timer interrupt. If the watchdog timer reset is enabled and the software does not reset the counter within the reset time

period (WDT0_CTRL.rst_period), the watchdog timer generates a system reset.

Figure 11-1 shows the block diagram of the watchdog timers.

Figure 11-1: Watchdog Timer Block Diagram

11.1 Features

• Sixteen programmable time periods for the watchdog interrupt

2

16

through 2

31

PCLK cycles

• Sixteen programmable time periods for the watchdog reset

2

16

through 2

31

PCLK cycles

• The watchdog timer counter is reset on all forms of reset

Loading...

Loading...