MAX32660 User Guide

Maxim Integrated Page 63 of 195

Enable low power mode wakeup (SLEEP, DEEPSLEEP and BACKUP) from an external GPIO event by completing the following

steps:

1. Set the polarity (rising or falling edge) by writing to the GPIO0_INT_POL[pin] field. The wakeup functionality uses

rising and falling edge detection circuitry that operates asynchronously and does not require an active clock. Dual-

edge mode is also an option to accomplish edge detection wakeup.

2. Clear pending interrupt flags by writing 0xFF to the GPIO0_INT_FL register.

3. Activate the GPIO wakeup function by writing 1 to GPIO0_WAKE_EN[pin].

4. Configure the power manager to use the GPIO as a wakeup source by writing to the appropriate Global Control

register (GCR).

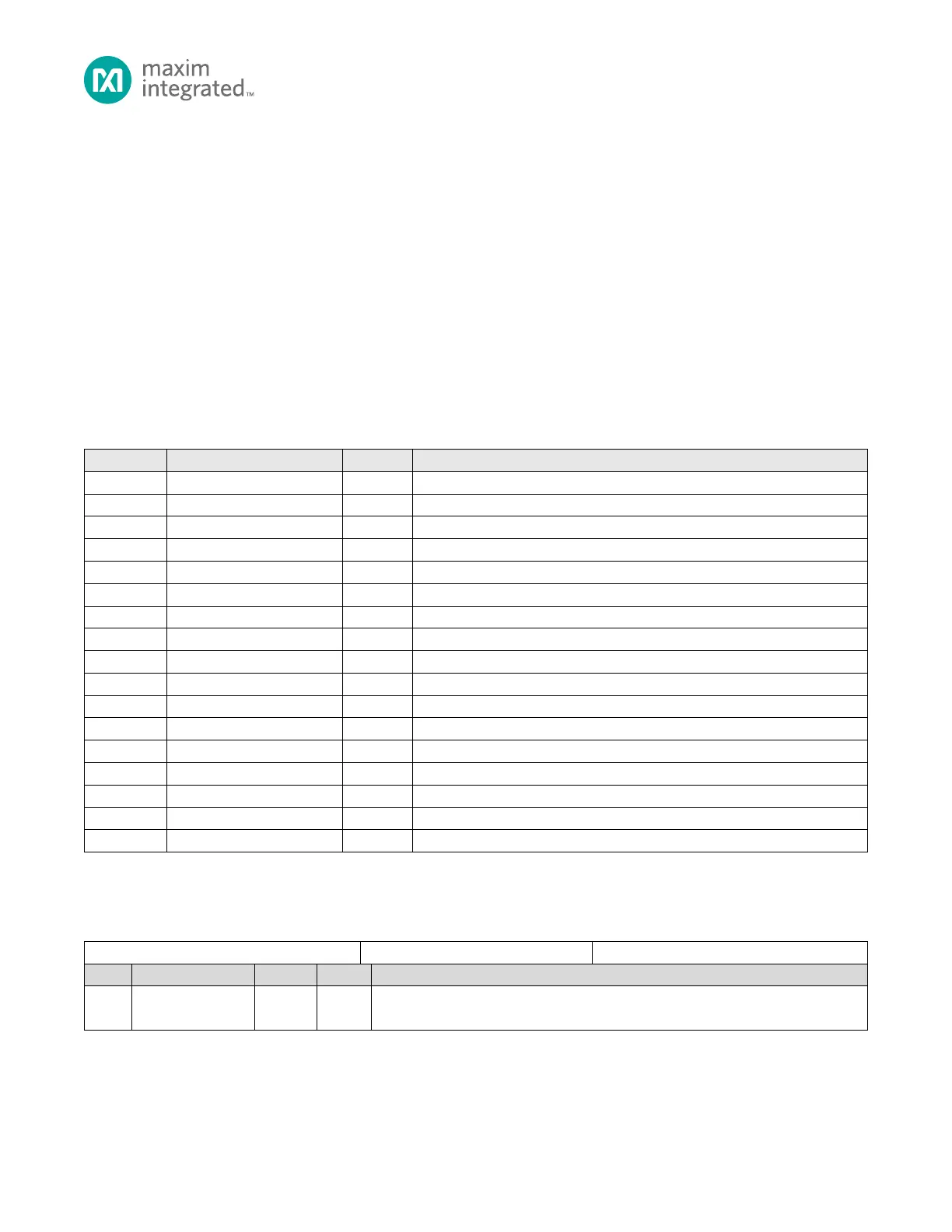

6.5 GPIO Registers

The GPIO0 base peripheral address is 0x4000 8000. Refer to Table 3-1: APB Peripheral Base Address Map for the addresses

of all APB mapped peripherals.

Table 6-8: GPIO Port 0 Registers

I/O and Alternate Function 1 Select Register

Interrupt Polarity Select Register

Interrupt Enable Register

Dual Edge Select Interrupt Register

Input Pullup/Pulldown Select Register

Alternate Function 2/3 Select Register

Input Hysteresis Enable Register

Slew Rate Select Register

Drive Strength Select 0 Register

Drive Strength Select 1 Register

Pullup/Pulldown Enable Register

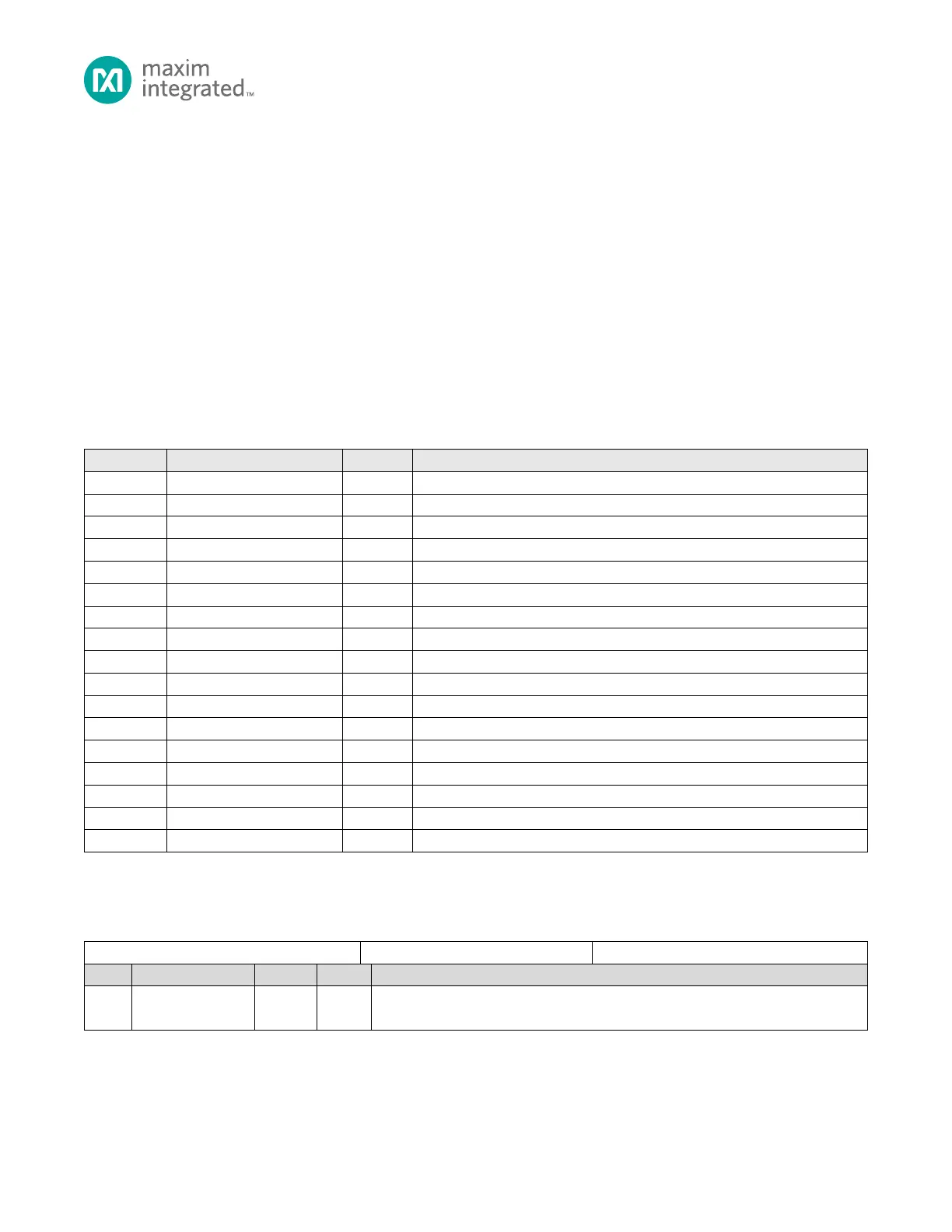

6.5.1 GPIO Register Details

Table 6-9: GPIO Alternate Function 0 Select Register

GPIO Alternate Function 0 Select Register

Reserved for Future Use

Do not modify this field.

Loading...

Loading...