MAX32660 User Guide

Maxim Integrated Page 189 of 195

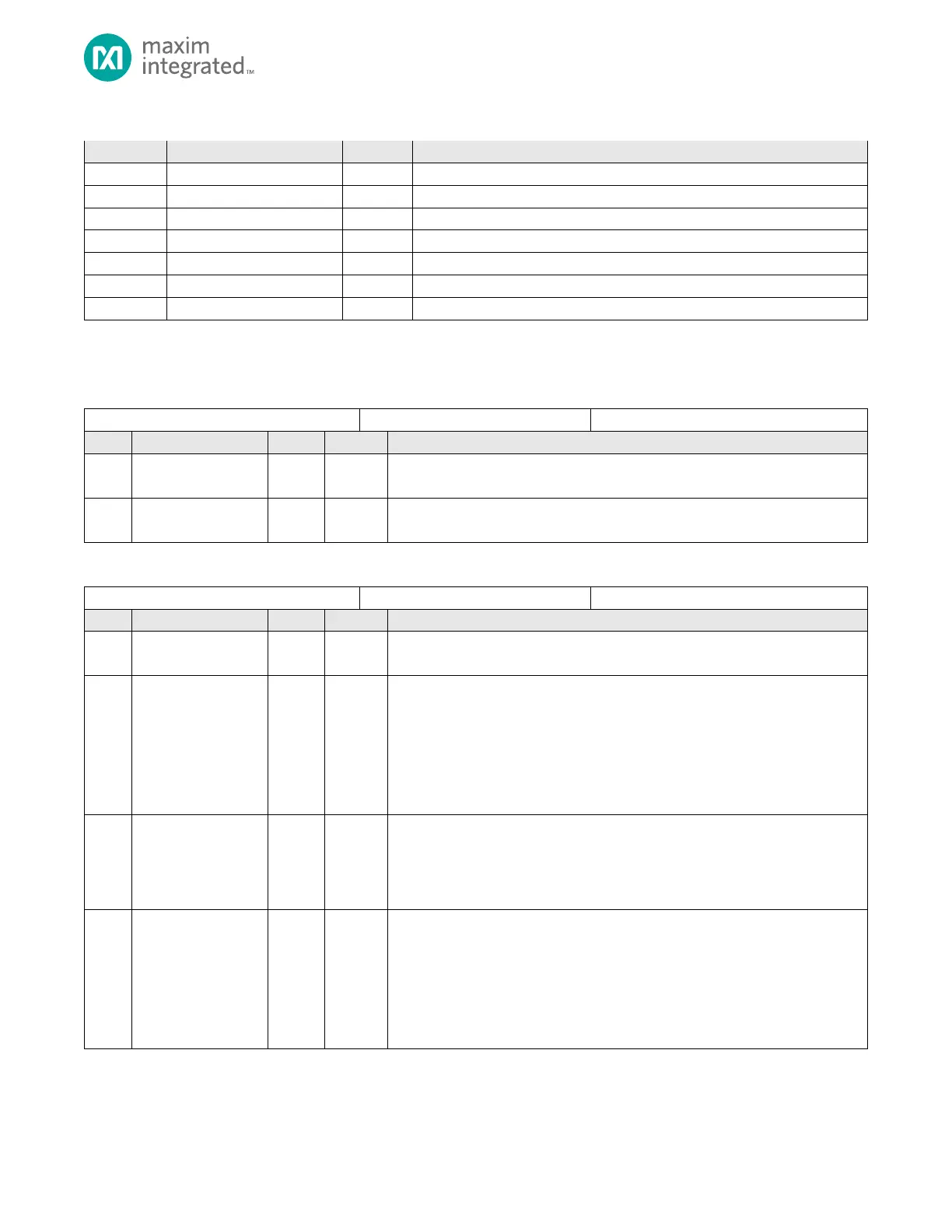

Table 14-5: SPIMSS Register Offsets, Access and Descriptions

SPIMSS Interrupt Flag Register

SPIMSS I

2

S Control Register

14.8.1 SPIMSS Register Details

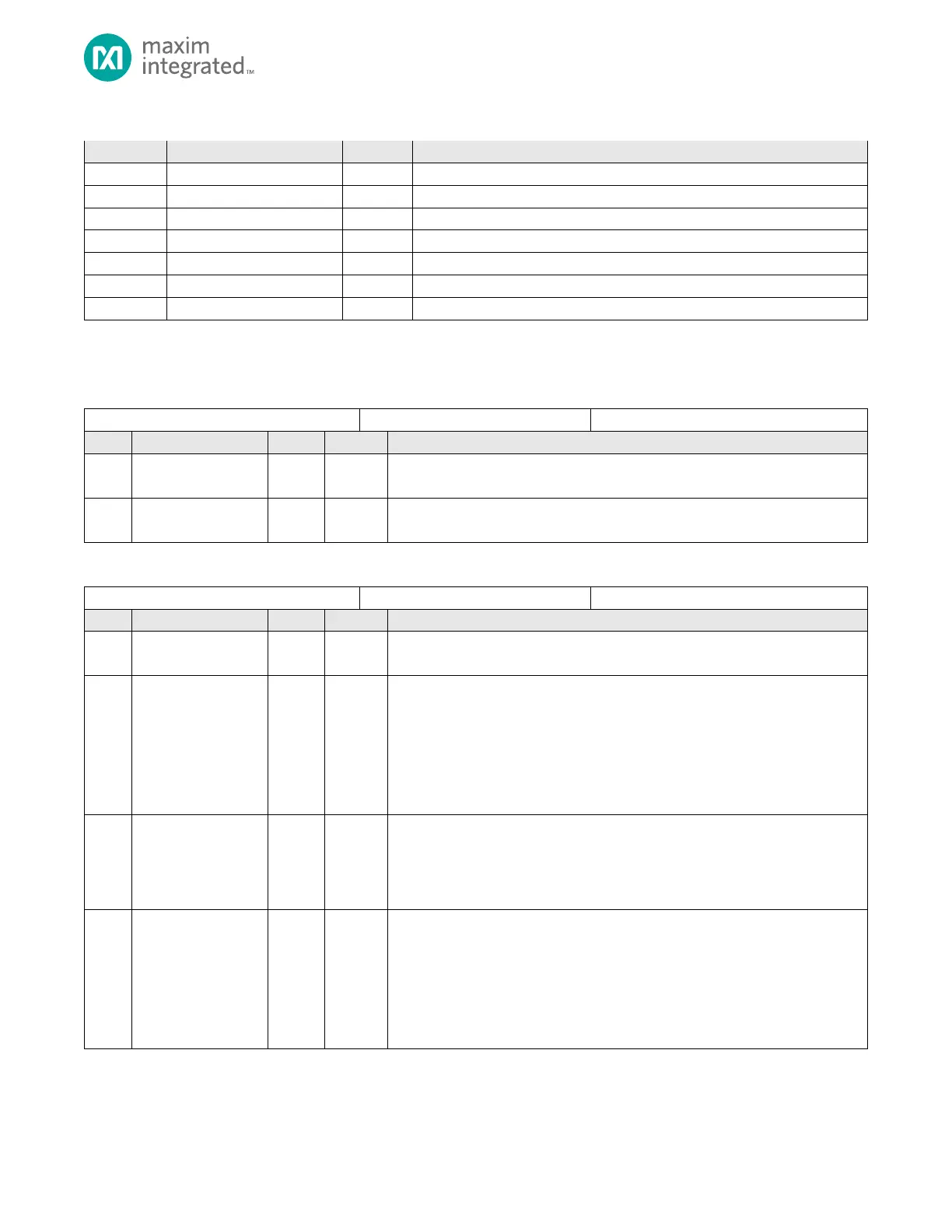

Table 14-6. SPIMSS Data Register

Reserved for Future Use

Do not modify this field.

SPIMSS Data

Refer to the SPI Data Movement section for details.

Table 14-7: SPIMSS Control Register

Reserved for Future Use

Do not modify this field.

Interrupt Request Enable

Set to enable interrupts for the SPIMSS peripheral.

0: SPIMSS (SPI1/I

2

S) interrupts are disabled.

1: SPI MSS (SPI1/I

2

S) interrupts are enabled. Interrupt requests are sent to the

Interrupt Controller

Note that if transmit or receive DMA is enabled, the transmit data complete

interrupt is disabled, but other interrupt sources are available.

Start SPI Interrupt

Setting this bit starts a SPIMSS interrupt request. Setting this bit also sets

SPIMSS_INT_FL.irq to 1. Setting this bit forces the SPIMSS to send an interrupt

request to the Interrupt Controller if SPIMSS_CTRL.irqe = 1. This bit is cleared by

writing a 0 to this bit or by writing a 1 to SPIMSS_INT_FL.irq.

Bit Rate Generator Timer Interrupt Request

Enable or disable the Bit Rate Generator if the SPIMSS is enabled

(SPIMSS_CTRL.enable = 1).

0: Clearing this bit disables the Bit Rate Generation timer function.

1: Setting this bit to 1 enables the Bit Rate Generation timer function and

enables the time-out interrupt.

Note: If SPIMSS_CTRL.enable = 0, this bit has no effect.

Loading...

Loading...