MAX32660 User Guide

Maxim Integrated Page 145 of 195

I

2

C Clock Low Time Register

I

2

C Clock High Time Register

I

2

C Hs-Mode Clock Control Register

I

2

C Slave Address Register

1.1.2 I

2

C Register Details

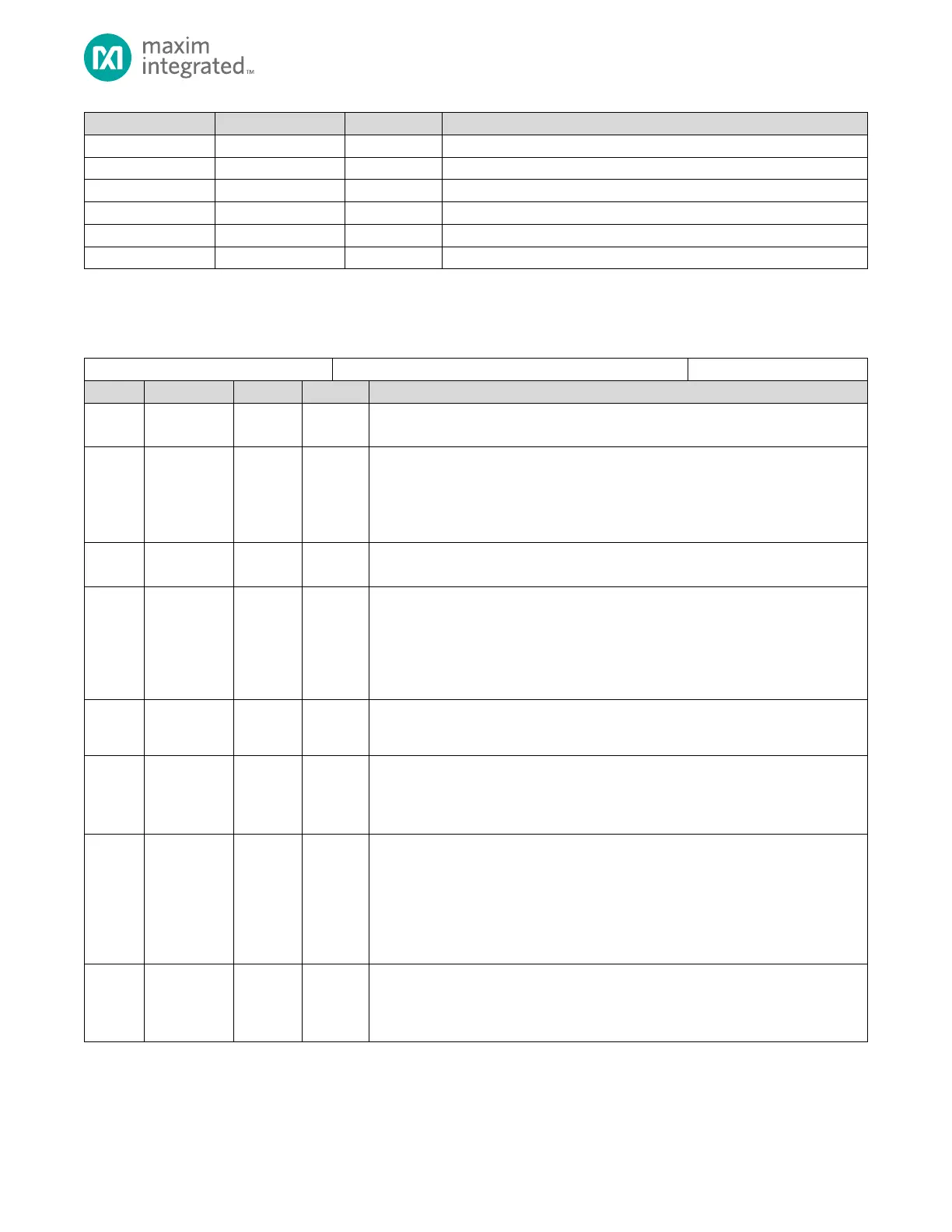

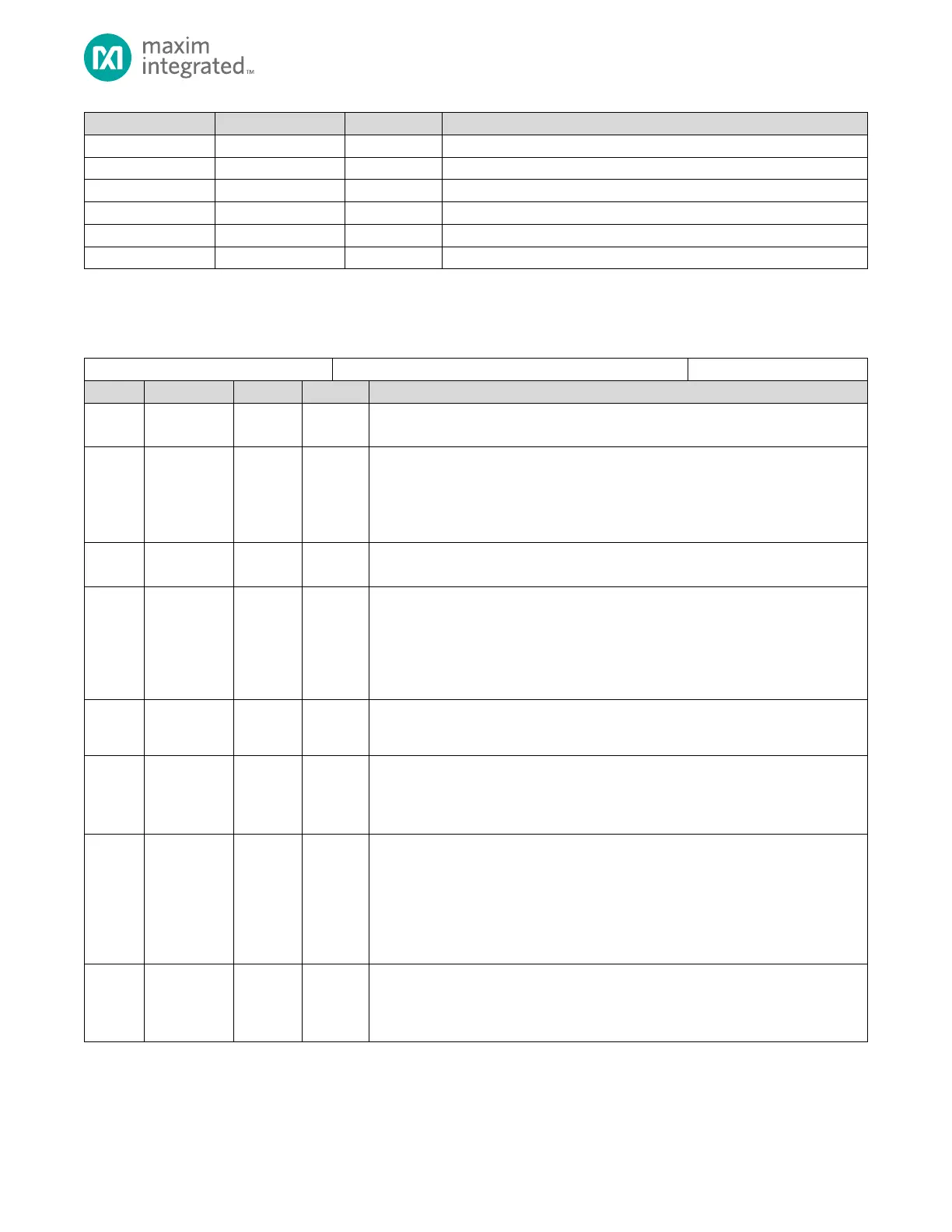

Table 12-4: I

2

C Control Registers 0

Reserved for Future Use

Do not modify this field.

High Speed Mode

Set this field to 1 to enable High-speed mode (Hs-mode) operation. This field must be

set to 0 for Standard, Fast or Fast-Plus operation.

0: Hs-mode not enabled.

1: Hs-mode enabled.

Reserved for Future Use

Do not modify this field.

SCL Push-Pull Mode Enable

Setting this field enables push-pull mode for the SCL hardware pin. This field should

not be set unless any external slave device will never actively drive SCL low.

0: SCL operates in standard I

2

C open-drain mode

1: SCL operates in push-pull mode without the need for a pull-up resistor. Only

recommended when in Master mode and external slaves will not drive SCL low.

SCL Clock Stretch Control

0: Enable Slave clock stretching

1: Disable Slave clock stretching

Read/Write Bit Status

Returns the logic level of the R/W bit on a received address match

(I2Cn_INTFL0.ami = 1) or general call match (I2Cn_INTFL0.gci = 1). This bit is valid for

three SCL clock cycles after the address match status flag is set.

Software output Enabled

When set, pins SDA and SCL are directly controlled by the fields I2Cn_CTRL0.sdao and

I2Cn_CTRL0.sclo, rather than the I

2

C controller. Setting this field to 1 enables software

bit bang control of I

2

C.

0: The I

2

C controller manages the SDA and SCL pins in hardware.

1: SDA and SCL are controller by firmware using the I2Cn_CTRL0.sdao and

I2Cn_CTRL0.sclo fields.

SDA Status

Returns the current logic level of the SDA pin.

0: SDA pin is logic low.

1: SDA pin is logic high.

Loading...

Loading...