This determines the maximum data width used during each read of the AHB

burst (byte, two bytes, or four bytes). The actual AHB width might be less if

DMAn_CNT is not great enough to supply all of the needed bytes.

7.5 Data Movement from the DMA FIFO to Destination

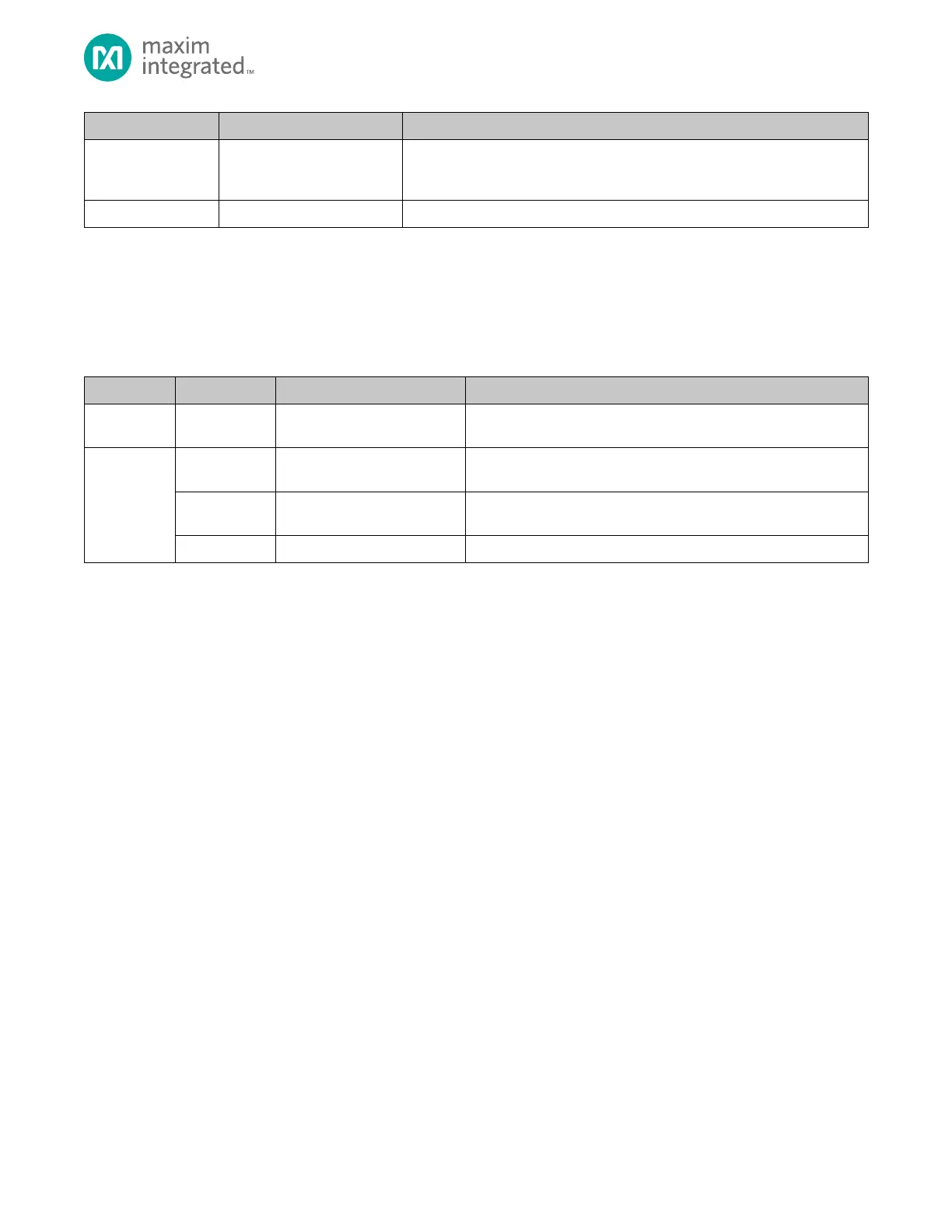

Table 7-5 shows the registers and bit fields used to control the burst movement of data out of the DMA FIFO. The

destination is a peripheral or memory.

Table 7-5: Data movement from the DMA FIFO to destination

This determines the maximum data width used during each write of

the AHB burst (one byte, two bytes, or four bytes).

7.6 Count-To-Zero (CTZ) Condition

When an AHB channel burst completes, the DMAC checks whether DMAn_CNT is decremented to 0. If it is, then a CTZ

condition is triggered.

At this point, there are two possible responses depending on the value of the DMAn_CFG.rlden bit.

If DMAn_CFG.rlden = 1, then automatic reload occurs as follows:

• The DMAn_SRC, DMAn_DST, and DMAn_CNT registers are loaded from the reload registers.

• The channel remains active and continues operating.

The channel uses the previously programmed configuration values and the reloaded source, destination and

count values.

If DMAn_CFG.rlden = 0, then the CTZ condition indicates the operation is complete and the following occurs:

• The channel is disabled, DMAn_CFG.chen = 0

• The channel status is set to disabled, DMAn_STAT.ch_st = 0.

7.7 Chaining Buffers

Use reload registers to chain buffers. Chaining buffers reduces the DMA ISR response time and allows DMA to service

requests without intermediate processing from the CPU.

Loading...

Loading...