MAX32660 User Guide

Maxim Integrated Page 129 of 195

11.8 Watchdog Timer Registers

The WDT0 base peripheral address is 0x4000 3000. Refer to Table 3-1: APB Peripheral Base Address Map for the addresses

of all APB mapped peripherals.

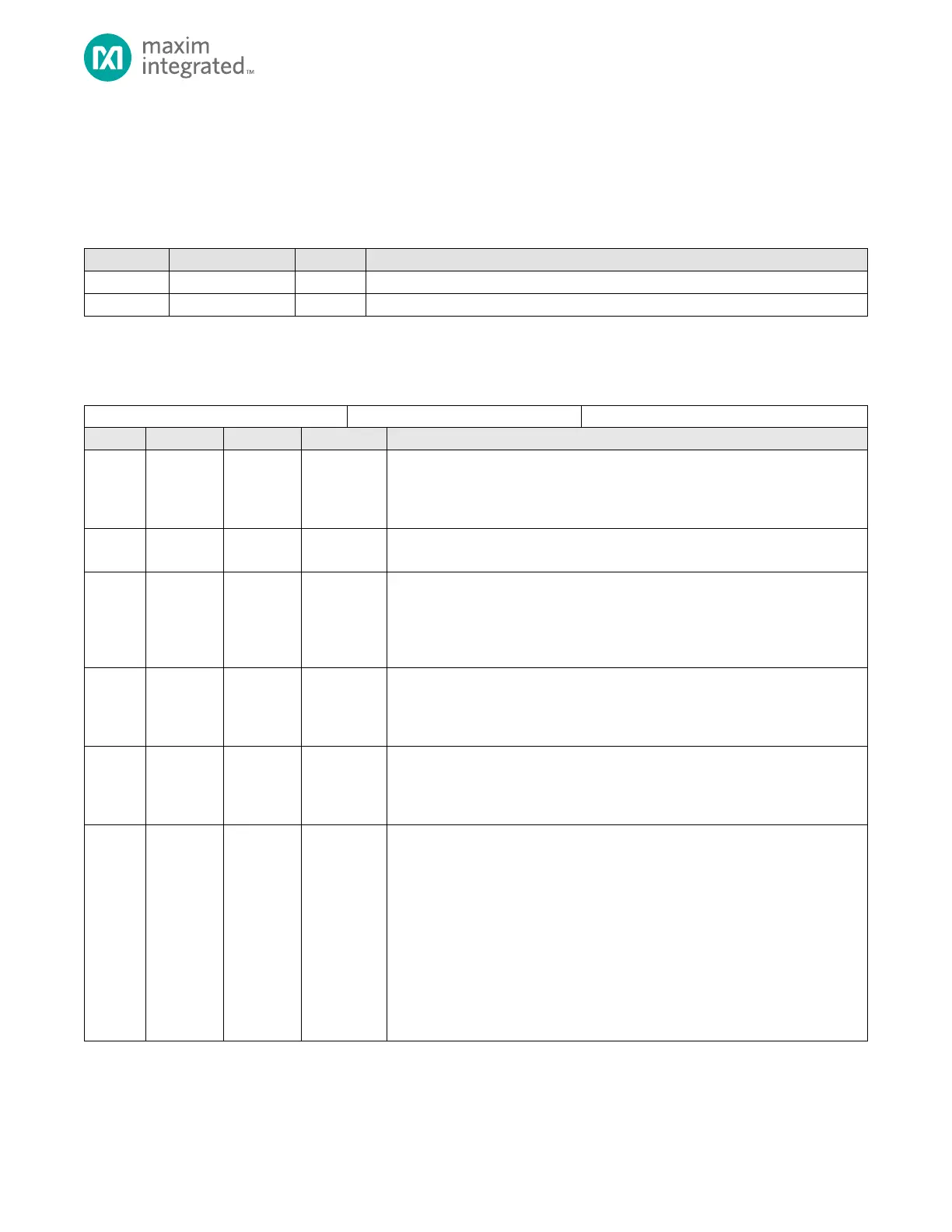

Table 11-2: Watchdog Timer Registers

Watchdog Timer 0 Control Register

Watchdog Timer 0 Reset Register

1.1.1 Watchdog Timer Register Details

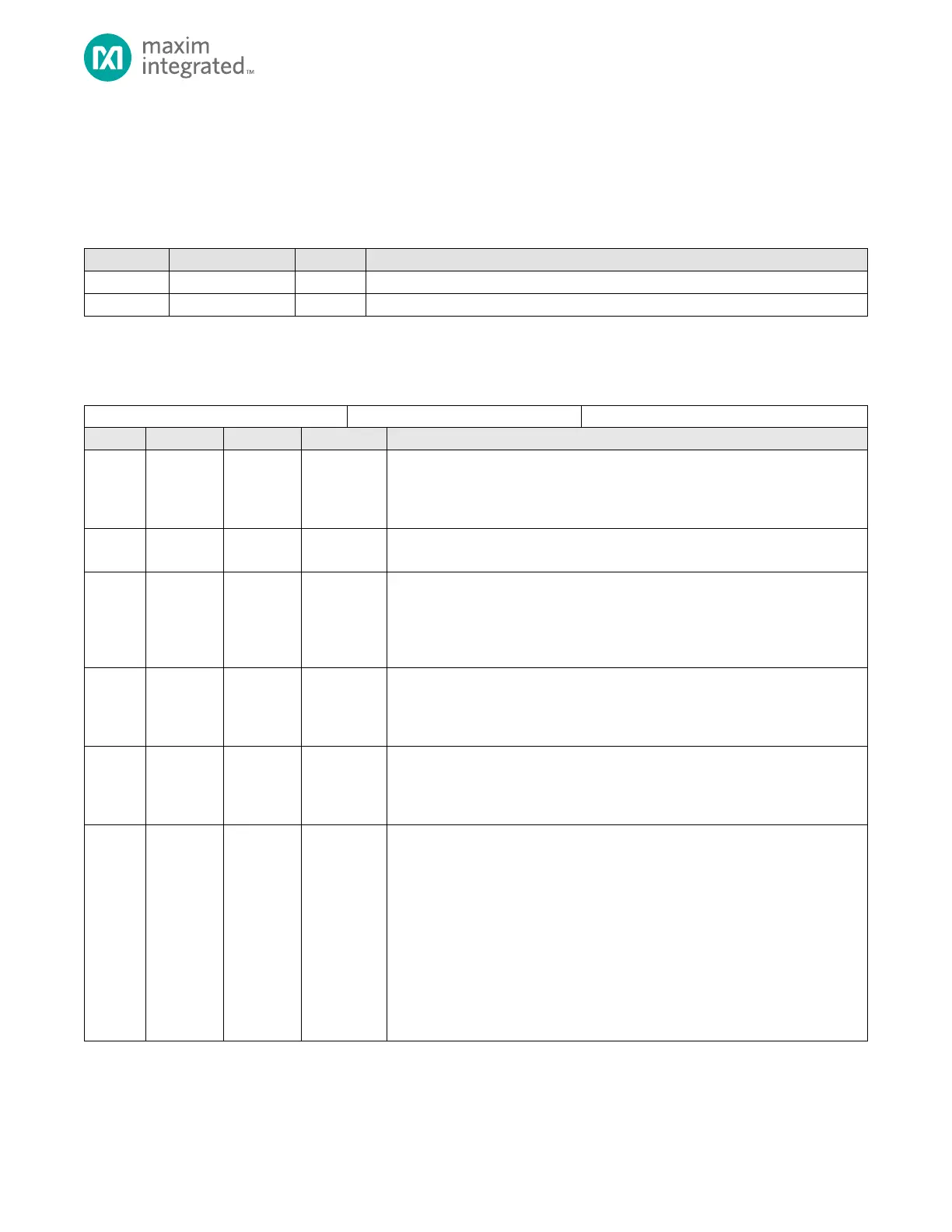

Table 11-3: Watchdog Timer Control Register

Watchdog Timer 0 Control Register

Reset Flag

If set a watchdog system reset occurred.

0: Watchdog did not cause reset event.

1: Watchdog reset occurred.

Reserved for Future Use

Do not modify this field.

Reset Enable

Enable/Disable system reset if the WDT0_CTRL.rst_period expires. Only reset by

power on reset.

0: Disabled

1: Enabled

Interrupt Enable

Enable or Disable the watchdog interrupt.

0: Disabled

1: Enabled

Interrupt Flag

If set, the watchdog interrupt period has occurred.

0: IRQ not pending

1: Interrupt period expired. Generates a WDT IRQ if WDT0_CTRL.int_en = 1.

Enable

Enable or disable the watchdog timer. Only reset by a power on reset. To enable

the watchdog timer, the following sequence of writes must be performed.

1) Write WDT0_RST: 0x0000 00A5

2) Write WDT0_RST: 0x0000 005A

3) Write WDT0_RST.wdt_en: 0x1

0: Disabled

1: Watchdog Timer Enabled. To set this field to 1, perform the sequence shown

above.

Note: This field is reset by a Power-On Reset event only. Other forms of reset do not

reset this field.

Loading...

Loading...