MAX32660 User Guide

Maxim Integrated Page 89 of 195

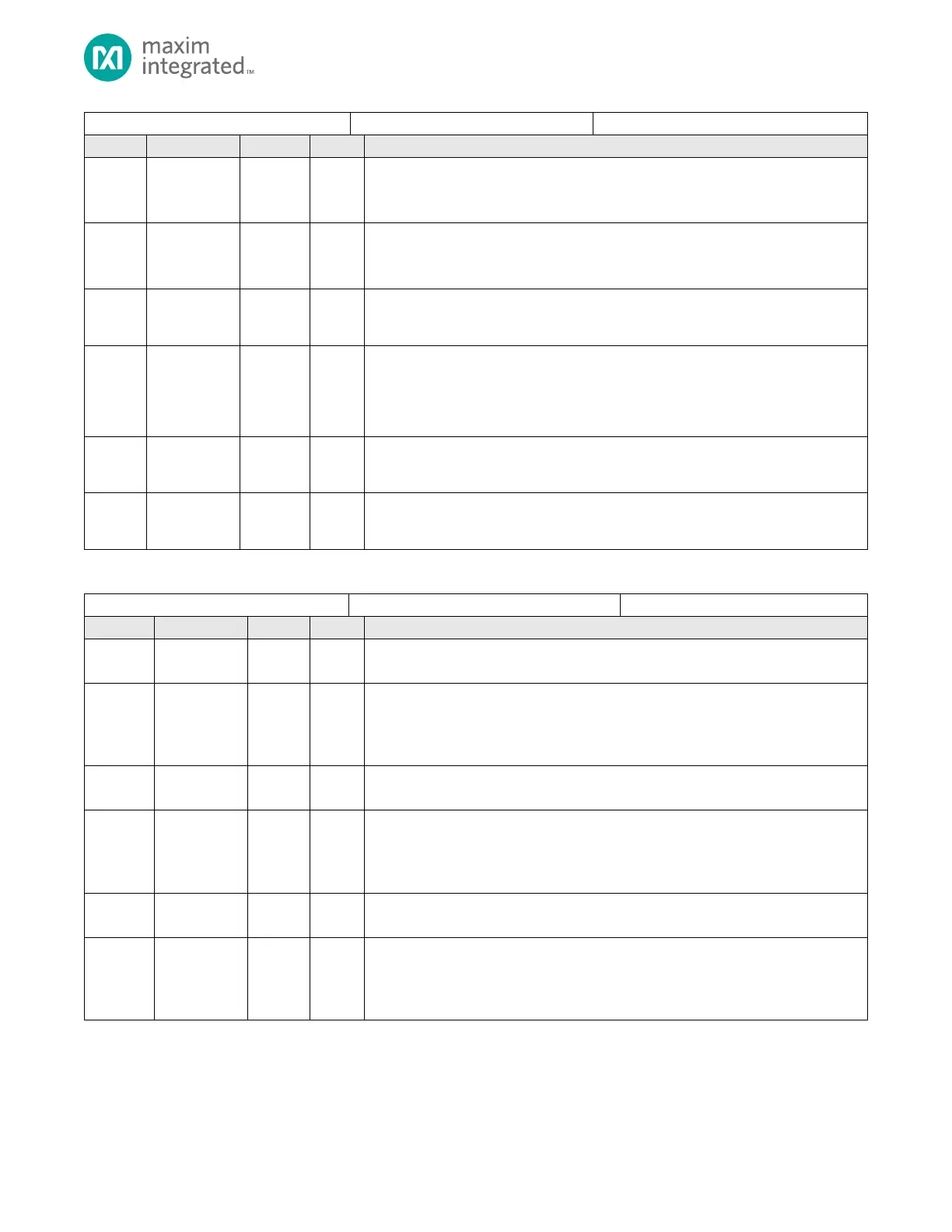

Receive FIFO Flush

Write 1 to flush the receive FIFO

Cleared to 0 by hardware when flush is completed

Transmit FIFO Flush

Write 1 to flush the Transmit FIFO

Cleared to 0 by hardware when flush is completed

Parity Level Select

0: Parity is based on number of 0 bits in the character.

1: Parity is based on number of 1 bits in the character.

Parity Mode Select

0: Even parity

1: Odd Parity

2: Mark parity

3: Space parity

Parity Enable

0: No parity

1: Parity enabled as charsize+1 bit

UART Enable

0: UART disabled. FIFOs are flushed, bit rate generator is off.

1: UART Enabled, bit rate generator is active.

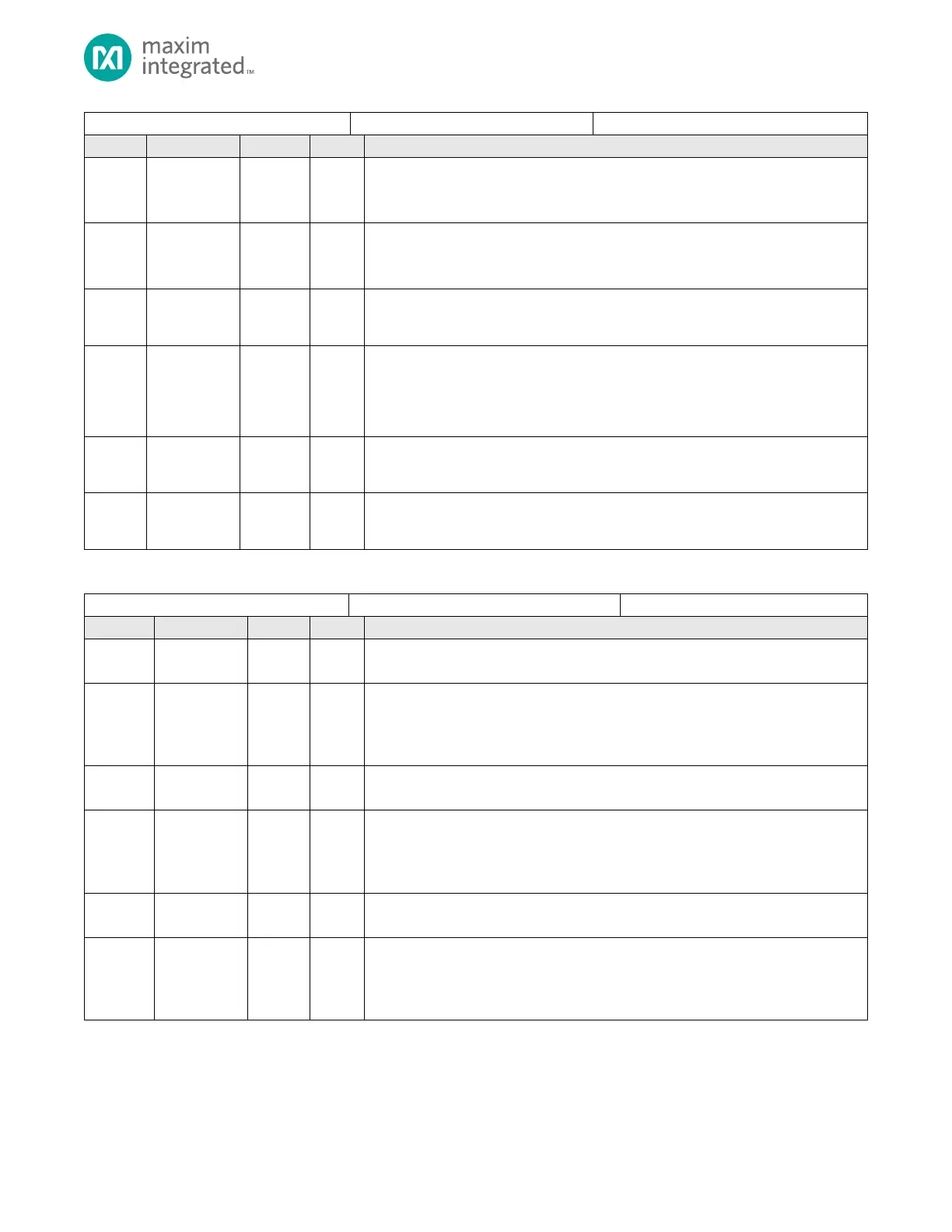

Table 8-4: UART Control 1 Register

Reserved for Future Use

Do not modify this field.

RTS RX FIFO Threshold Level

When the RX FIFO level is equal to or greater than this level, assert RTS output signal

to inform the transmitting UART to stop sending data to this UART.

Valid values are from 0 to 32.

Reserved for Future Use

Do not modify this field.

TX FIFO Threshold Level

When the TX FIFO level is less than or equal to this level the UARTn_INT_FL.tx_fifo_lvl

interrupt flag is set.

Valid values are from 0 to 32.

Reserved for Future Use

Do not modify this field.

RX FIFO Threshold Level

When the RX FIFO reaches this level or higher the UARTn_INT_FL.rx_fifo_lvl interrupt

flag is set.

Valid values are from 0 to 32.

Loading...

Loading...