MAX32660 User Guide

Maxim Integrated Page 88 of 195

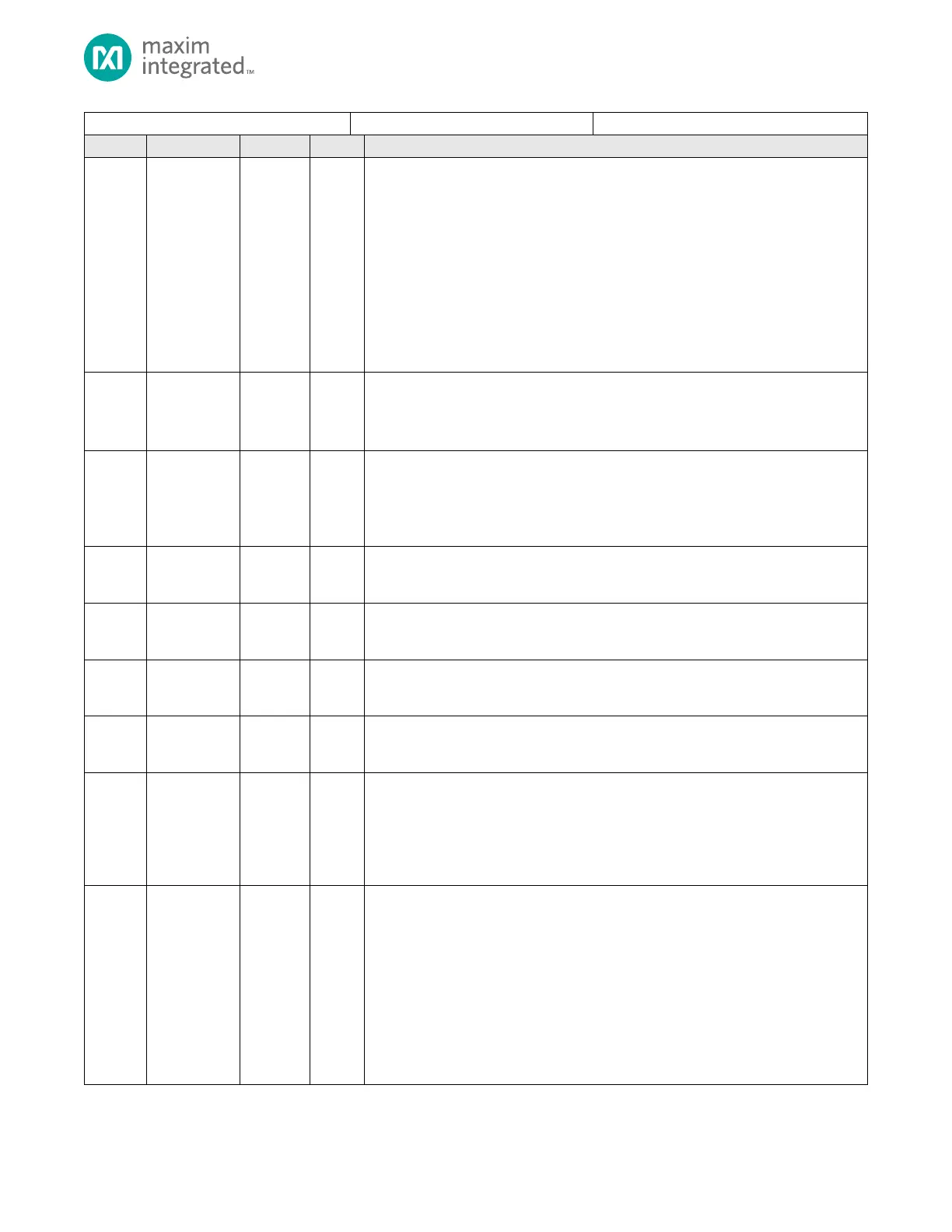

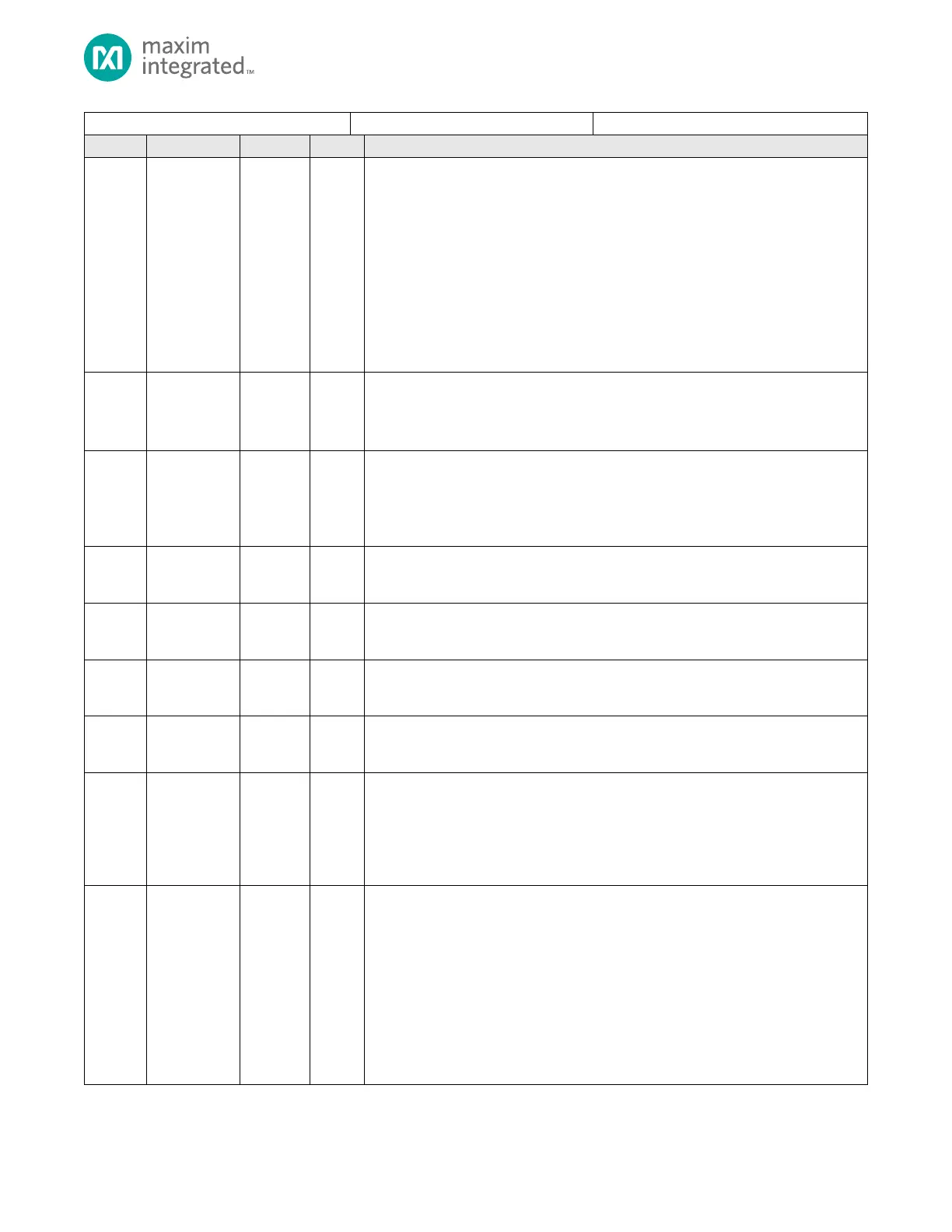

RX Timeout Frame Count

Set this field to the number of frames before a Receive Timeout occurs. If the RX FIFO

contains data, a RX Timeout condition occurs if the time for the number of frames in

this register passes without the FIFO receiving any new data. If a timeout occurs, the

hardware sets the receive timeout flag to 1 (UARTn_INT_FL.rxto = 1).

0: 256

1: 1

2: 2

3: 3

254: 254

255: 255

Bit Rate Clock Source Select

Selects the bit rate clock,

0: Peripheral Clock,

1: Reserved for Future Use

Transmit BREAK Frame

Set this field to 1 to send a BREAK frame. A BREAK frame transmits a character with all

bits set to 0.

0: Normal UART operation.

1: Transmit BREAK frame.

Null Modem Support

0: Normal operation for RTS/CTS and TXD/RXD

1: Null Modem Mode: RTS/CTS swapped, TXD/RXD swapped

RTS/CTS Polarity

0: RTS/CTS asserted is 0

1: RTS/CTS asserted is 1

Hardware Flow Control Enable

0: Hardware flow control disabled.

1: Hardware RTS/CTS flow control enabled.

STOP Bit Mode Select

0: 1 STOP bit.

1: 1.5 STOP bits for 5-bit character size or 2 STOP bits for all other character sizes

Character Size

Set the number of data bits per frame.

0: 5 data bits

1: 6 data bits

2: 7 data bits

3: 8 data bits

Frame or Bit Accuracy Select

This field selects between either Frame Accuracy or Bit Accuracy for transmitting data.

Frame Accuracy: Individual frame bit durations may be varied by hardware to meet

the target frame period.

Bit accuracy: Bit width is fixed by hardware. The frame accuracy of data transmitted

may be reduced if bit accuracy is prioritized.

0: Frame accuracy.

1: Bit accuracy.

Note: A frame includes the start, stop, all data bits, and parity bit/bits for the character

being transmitted.

Loading...

Loading...