MAX32660 User Guide

Maxim Integrated Page 191 of 195

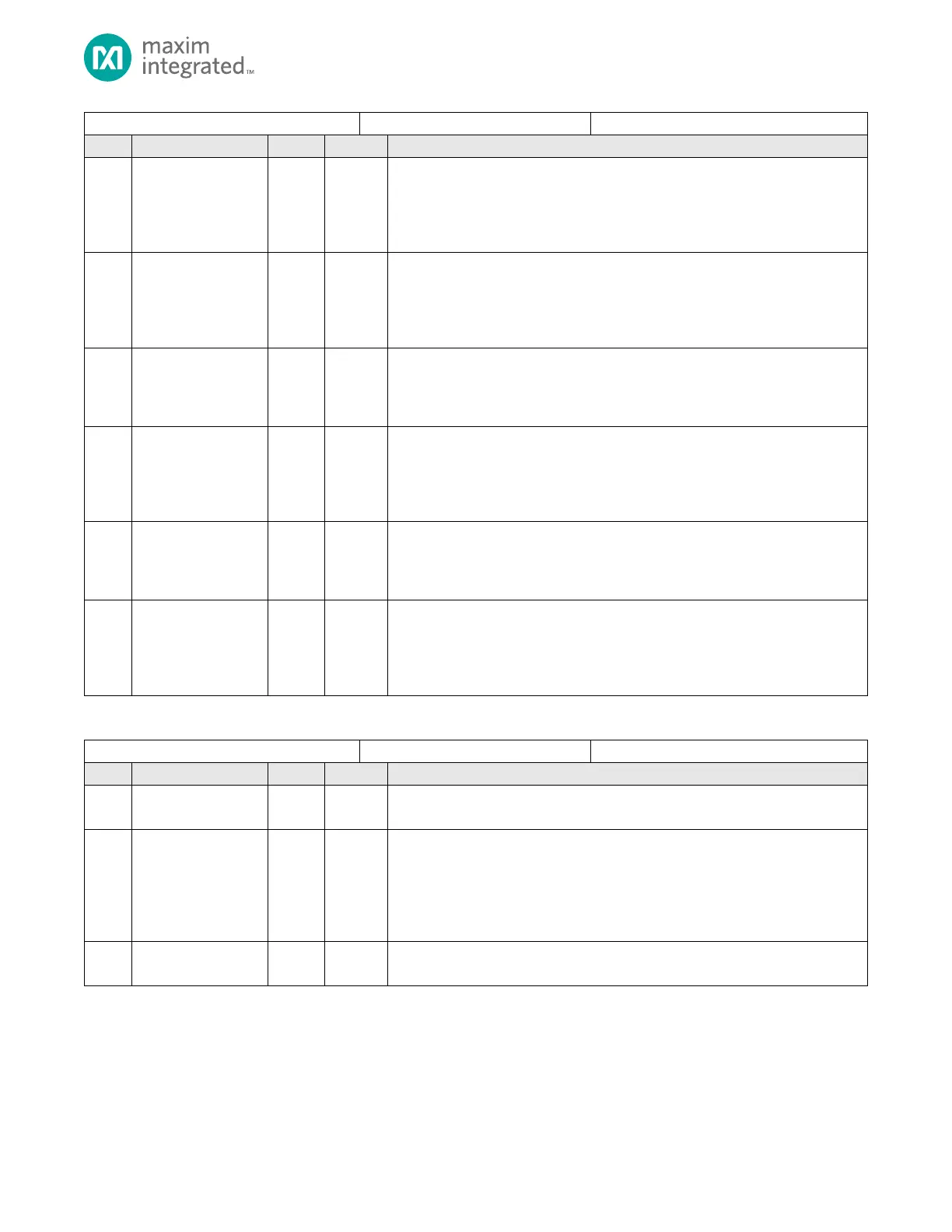

SPIMSS Interrupt Flag Register

Collision Flag

This bit is set by hardware when a multi-master collision (mode fault) occurs.

Write 1 to clear.

0: No multi-master collision has occurred

1: A multi-master collision has occurred

Slave Mode Transaction Abort Flag

This bit is set by hardware when a slave mode transaction abort occurs. Write 1 to

clear.

0: No slave mode transaction abort has occurred

1: A slave mode transaction abort has occurred

Receive Overrun Flag

This bit is set by hardware when a receive FIFO overrun occurs. Write 1 to clear.

0: No FIFO overrun has occurred

1: A FIFO overrun has occurred.

Transmit Underrun Flag

This bit is set by hardware to indicate a transmit FIFO underrun has occurred.

Write 1 to clear.

0: No FIFO underrun has occurred

1: A FIFO underrun has occurred

Transmit Status

This field reads 1 if a SPIMSS data transmission is currently in progress.

0: No data transmission currently in progress.

1: Data transmission currently in progress

Slave Select

If the SPI is in slave mode, this bit indicates if the SPI is selected. If the SPI is in

master mode, this bit has no meaning.

0: Slave SPI is selected

1: Slave SPI is not selected

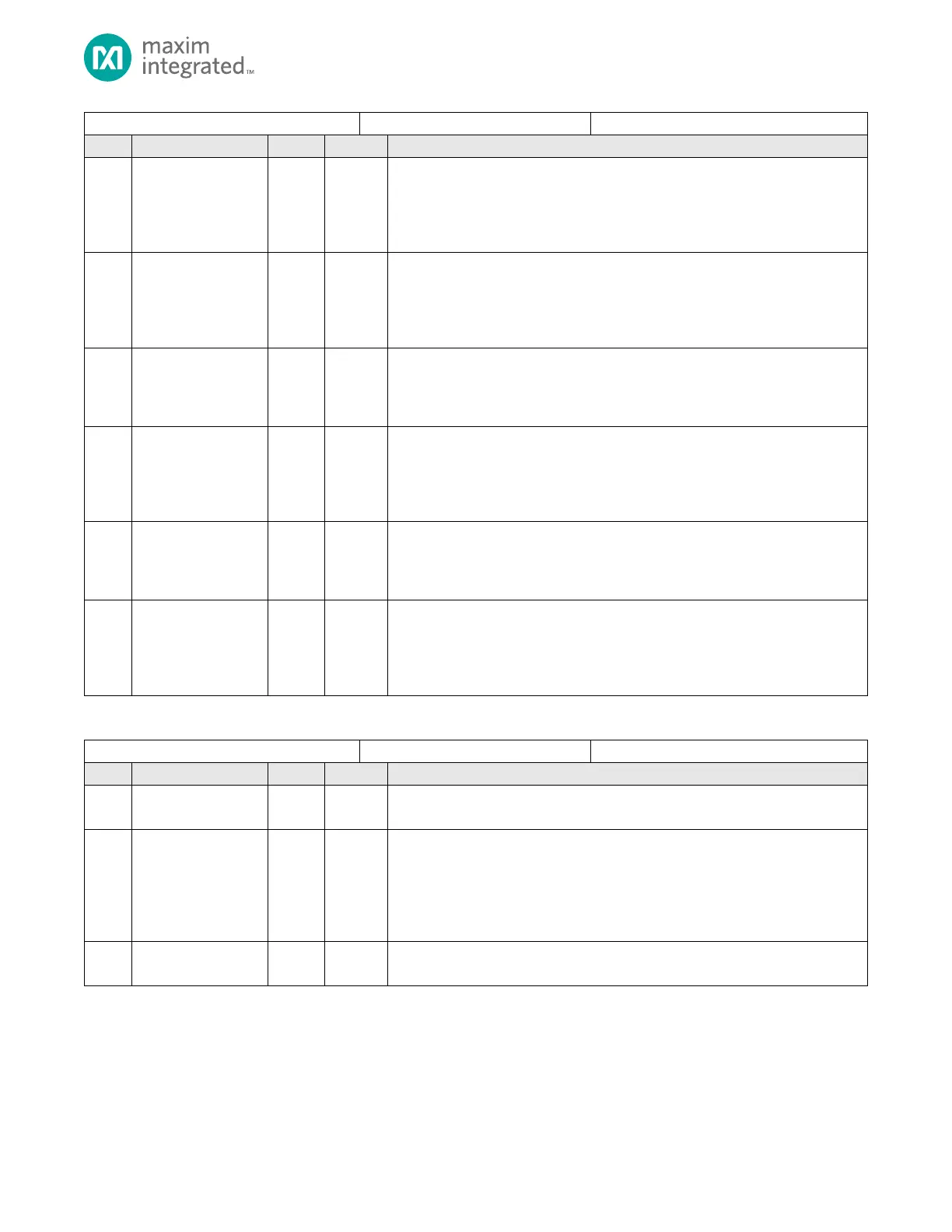

Table 14-9: SPIMSS Mode Register

Reserved for Future Use

Do not modify this field.

Transmit Data Alignment

Selects left or right alignment when data is loaded into the SPIMSS_DATA.data

field for transmission if the character size is less than 16-bits.

0: Data is LSB aligned with the unused bits set to 0 up to the MSB (right aligned)

1: Data is MSB aligned with the unused bits set to 0 down to the LSB (left

aligned)

Reserved for Future Use

Do not modify this field.

Loading...

Loading...