MAX32660 User Guide

Maxim Integrated Page 156 of 195

I

2

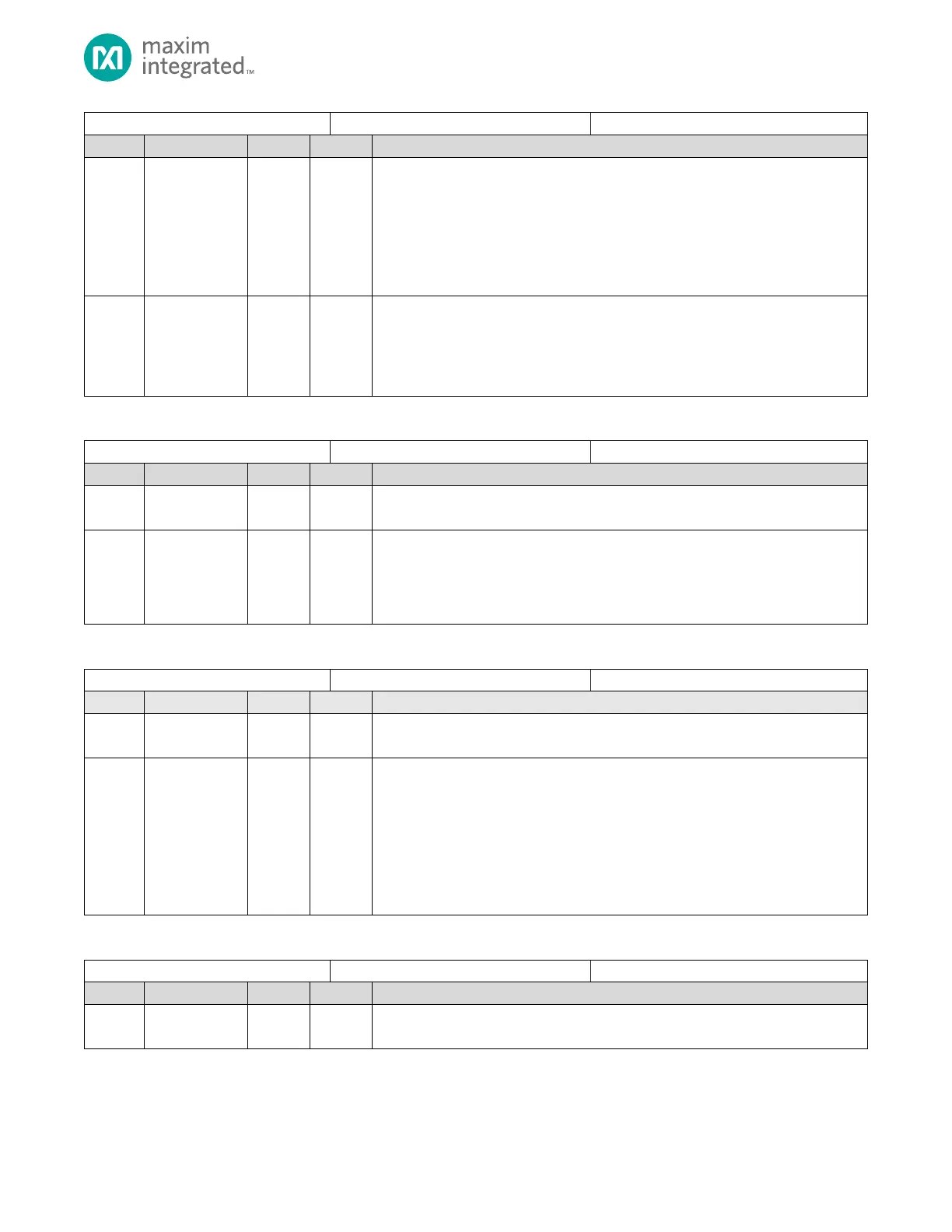

C Master Mode Control Register

Send Repeated START Condition

After sending data to a slave, instead of sending a STOP condition the master may

send another START to retain control of the bus.

0: Repeated start condition complete or inactive.

1: Send a Repeated START

Note: This bit is automatically cleared by hardware when the repeated START

condition begins.

Start Master Mode Transfer

0: Master mode transfer inactive.

1: Start Master Mode Transfer

Note: This bit is automatically cleared by hardware when the transfer is completed or

aborted.

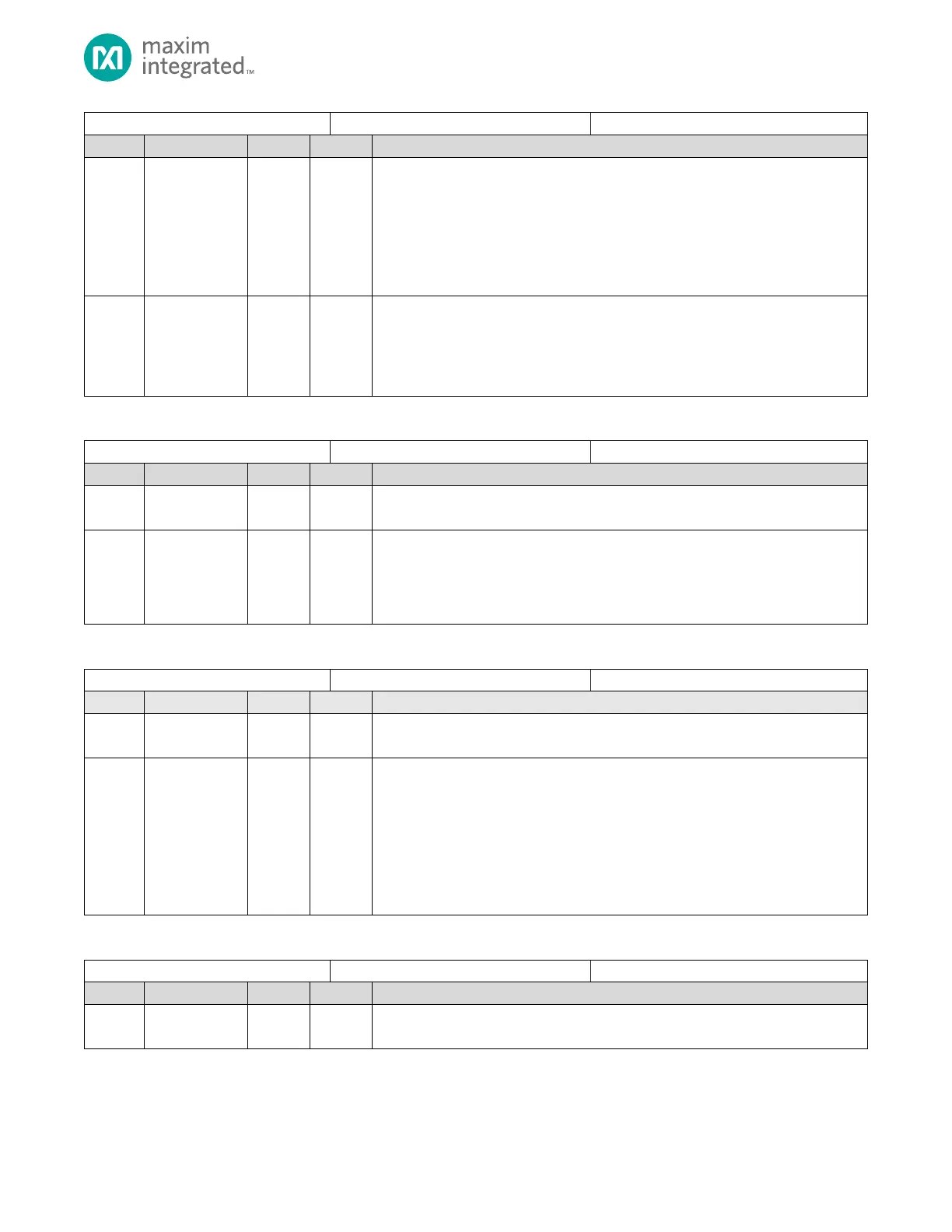

Table 12-17: I

2

C SCL Low Control Register

Reserved for Future Use

Do not modify this field.

Clock Low Time

In Master Mode, this configures the SCL low time.

Note: 0 is not a valid setting for this field.

Table 12-18: I

2

C SCL High Control Register

I

2

C Clock High Control Register

Reserved for Future Use

Do not modify this field.

Clock High Time

In Master Mode, this configures the SCL high time.

In both Master and Slave Mode, this also configures the time SCL is held low after

new data is loaded from the TX FIFO or after firmware clears irxmi during Interactive

Receive Mode.

Note: 0 is not a valid setting for this field.

Table 12-19: I

2

C Timeout Registers

Reserved for Future Use

Do not modify this field.

Loading...

Loading...