MAX32660 User Guide

Maxim Integrated Page 36 of 195

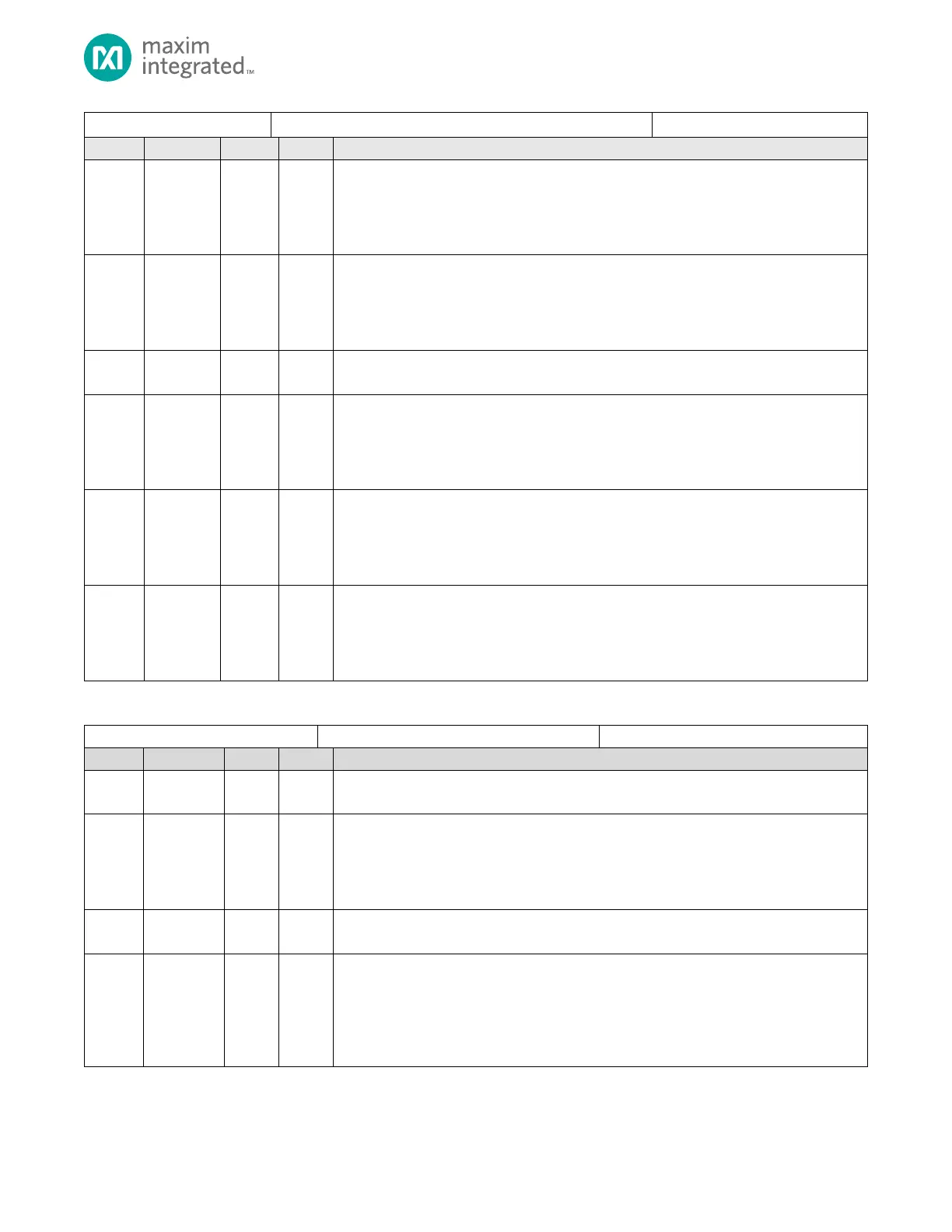

Timer1 Reset

Write 1 to reset the peripheral state to the reset default state. When complete this field will

read 0.

0: TMR1 peripheral not in reset.

1: Write 1 to reset the TMR1 peripheral.

Timer0 Reset

Write 1 to reset the peripheral state to the reset default state. When complete this field will

read 0.

0: TMR0 peripheral not in reset.

1: Write 1 to reset the TMR0 peripheral.

Reserved for Future Use

Do not modify this field.

GPIO0 Reset

Write 1 to reset the peripheral state to the reset default state. When complete this field will

read 0.

0: GPIO peripheral not in reset.

1: Write 1 to reset the GPIO peripheral.

Watchdog Timer 0 Reset

Write 1 to reset the peripheral state to the reset default state. When complete this field will

read 0.

0: WDT0 peripheral not in reset.

1: Write 1 to reset the WDT0 peripheral.

Standard DMA Reset

Write 1 to reset the peripheral state to the reset default state. When complete this field will

read 0.

0: Standard DMA peripheral not in reset.

1: Write 1 to reset the Standard DMA peripheral.

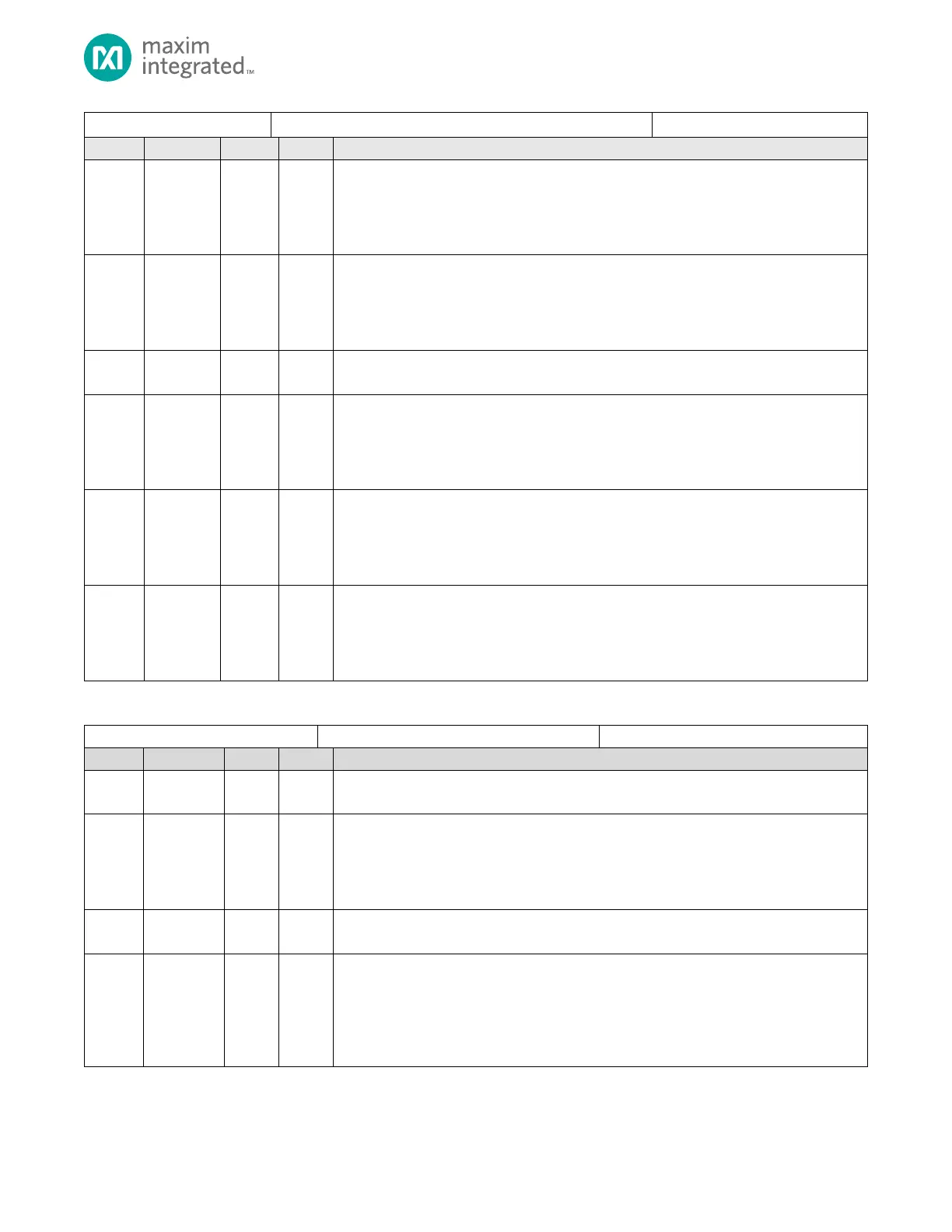

Table 4-15: System Clock Control Register

System Clock Control Register

Reserved for Future Use

Do not modify this field.

8kHz Internal Oscillator Ready Status

On POR or System Reset this field reads 0 until the 8kHz low-frequency oscillator is ready for

use.

0: Not ready or not enabled.

1: Oscillator ready.

Reserved for Future Use

Do not modify this field.

High-Frequency Internal Oscillator Ready

On POR or System Reset this field reads 0 until the HFIO oscillator is ready. If the HFIO is

disabled (GCR_CLK_CTRL.hirc_en = 0) and firmware enables it (GCR_CLK_CTRL.hirc_en = 1),

reading this field will return 0 until the HFIO is ready for use.

0: Oscillator not ready or not enabled.

1: Oscillator ready.

Loading...

Loading...