MAX32660 User Guide

Maxim Integrated Page 33 of 195

4.10.3 RAM Low Power Modes

RAM can be placed in a low power mode, referred to as Light Sleep, using register GCR_MEM_CTRL, Memory Clock Control.

Light Sleep gates off the clock to the RAM and makes the RAM unavailable for read/write operations. The RAM contents are

retained during Light Sleep mode. Light Sleep is available for the internal Data RAM blocks as well as for the ICC0 cache

RAM. Turning off Light Sleep mode for a memory enables Read/Write to that memory range.

RAM can also be shut down for power savings using the register PWRSEQ_LPMEMSD, RAM Shut Down Control. This

conserves power by gating off the power and clock to the RAM. This invalidates the contents of the RAM and the RAM is

not accessible until the RAM shutdown mode is disabled. When enabling a RAM partition from a shutdown state, the RAM

contents are cleared.

4.11 Global Control Registers (GCR)

The GCR base peripheral address is 0x4000 0000. Refer to Table 3-1: APB Peripheral Base Address Map for the addresses of

all APB mapped peripherals.

The Global Control Registers are only reset on a System Reset, Watchdog Timer Reset and a Power-On Reset. Soft Reset and

Peripheral Reset do not affect these registers.

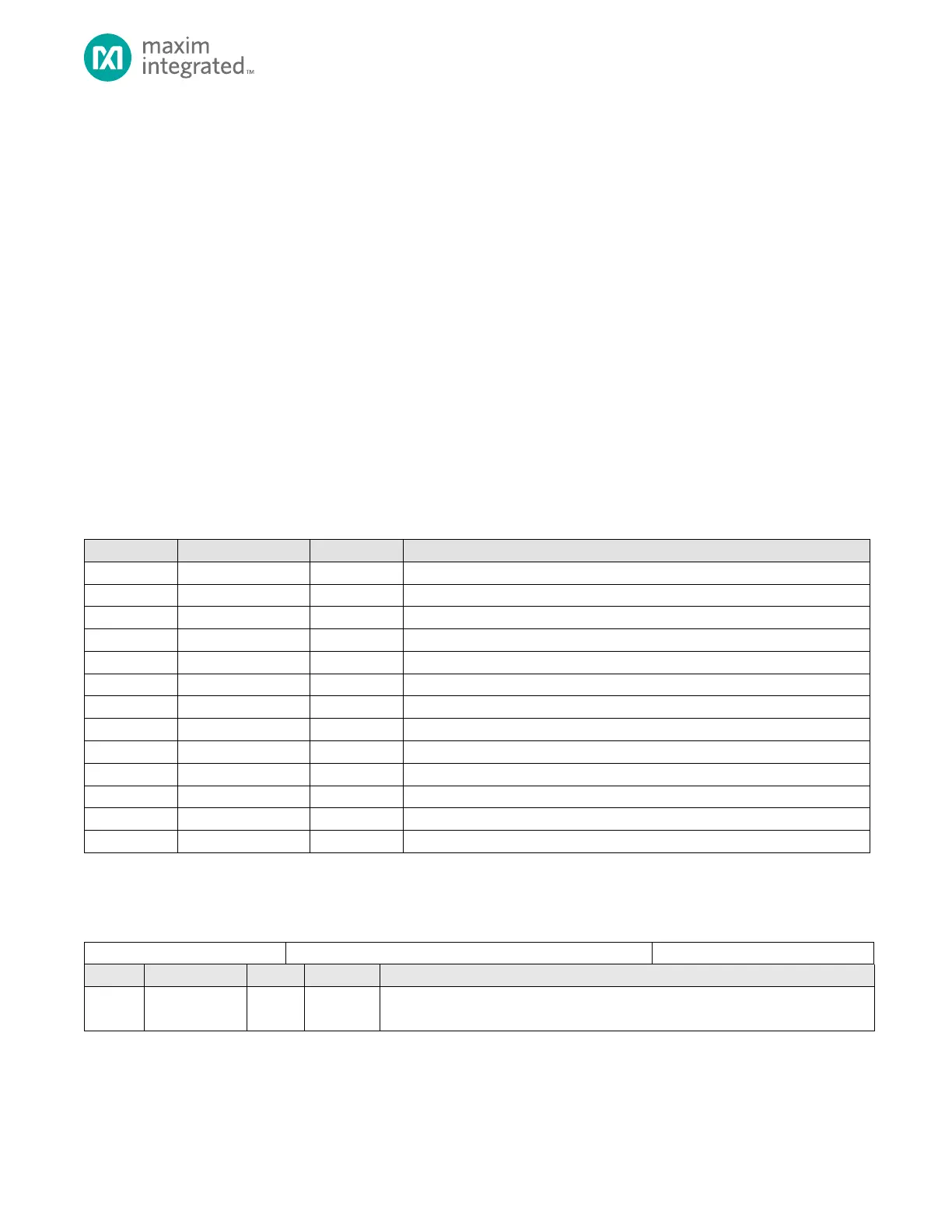

Table 4-12: Global Control Registers, Offsets and Descriptions

Loading...

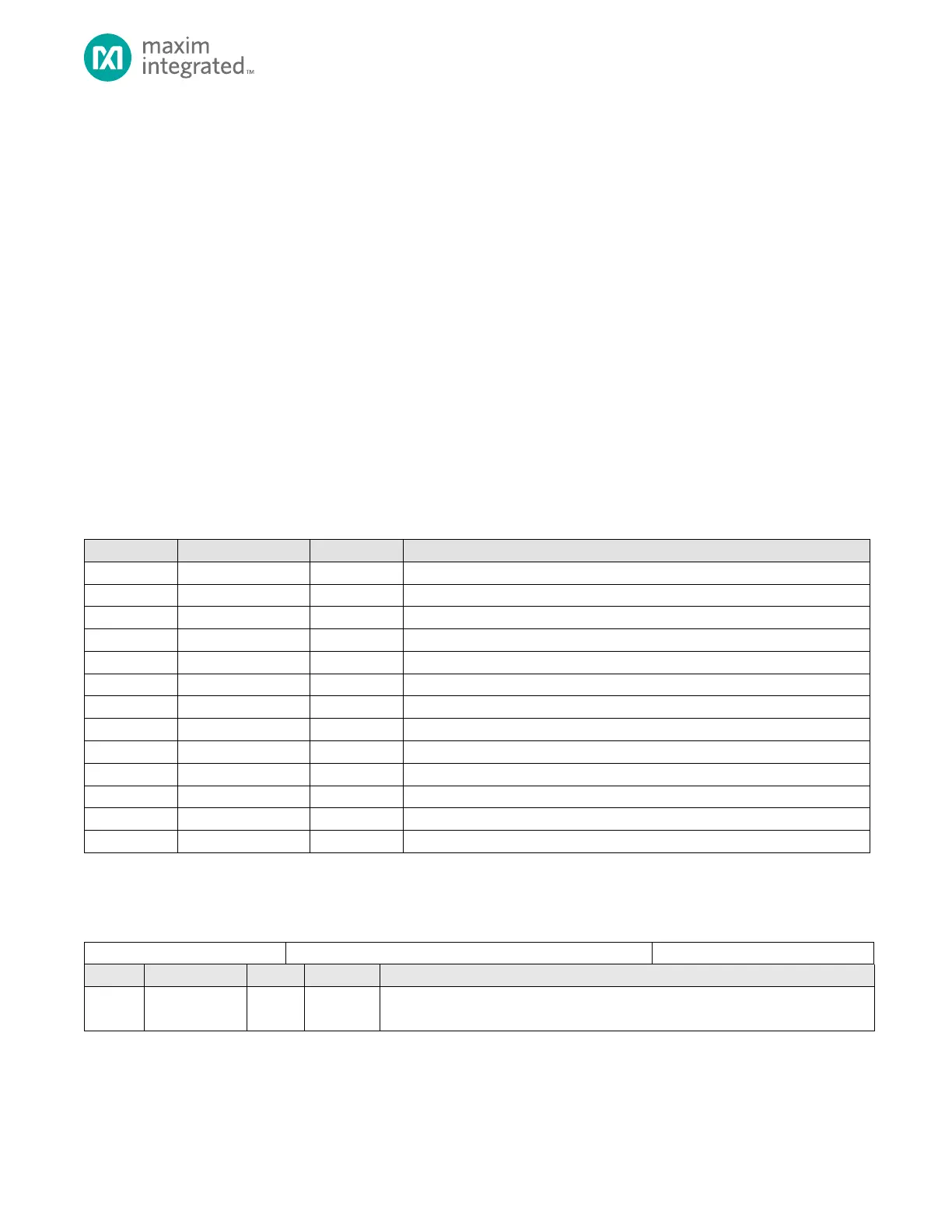

Loading...