MAX32660 User Guide

Maxim Integrated Page 81 of 195

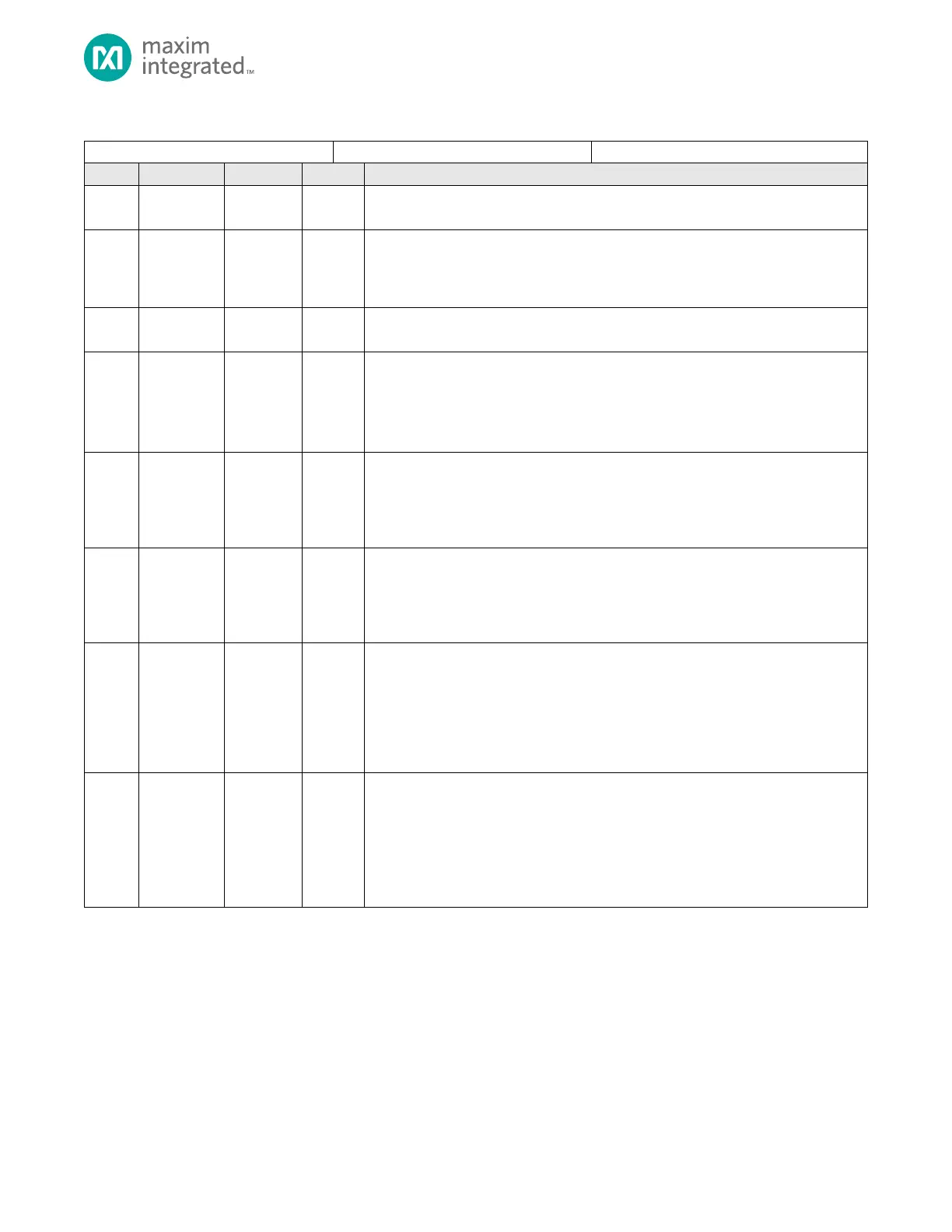

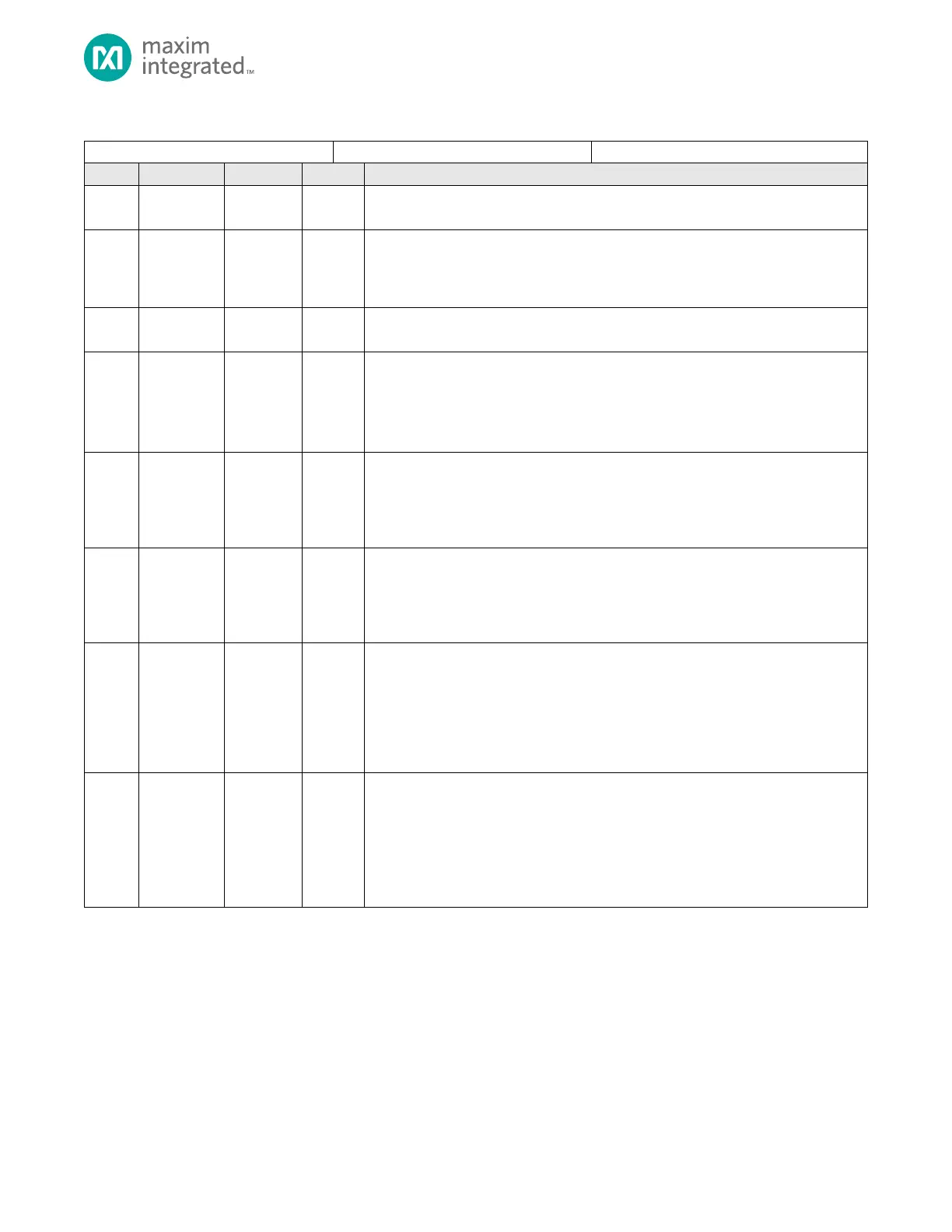

Table 7-12: DMA Status Register

Reserved for Future Use

Do not modify this field.

Time-Out Status

A time-out occurred if this field reads 1. Write 1 to clear.

0: No time out

1: A time out has occurred

Reserved for Future Use

Do not modify this field.

Bus Error

If this bit reads 1, an AHB abort occurred and the channel was disabled by hardware.

Reading this bit indicates the following:

0: No error found

1: An AHB bus error occurred

Reload Status

This bit is set by hardware when reload is enabled and a reload occurred. Write 1 to

clear.

0: Reload event has not occurred.

1: Reload event occurred.

CTZ Status

This bit is set by hardware when a Count-to-zero (CTZ) has occurred, if enabled. Write

1 to clear.

0: CTZ has not occurred

1: CTZ has occurred

Channel Interrupt

This field is set when any enabled channel interrupt occurs. When this field is set,

examine the other fields in this register, DMAn_STAT, to determine the cause of the

Channel Interrupt. Clearing the status bits in this register clears this field. This field is

read-only.

0: No channel interrupt pending.

1: Channel Interrupt pending.

Channel Status

This bit is used to indicate when it is safe to change the configuration, address, and

count registers for the channel. This field is read-only.

Hardware clears this bit automatically when the channel is not active. When hardware

clears this bit, hardware also clears the DMAn_CFG.chen bit.

0: Channel configuration can be changed.

1: Channel not safe to change configuration.

Loading...

Loading...