MAX32660 User Guide

Maxim Integrated Page 94 of 195

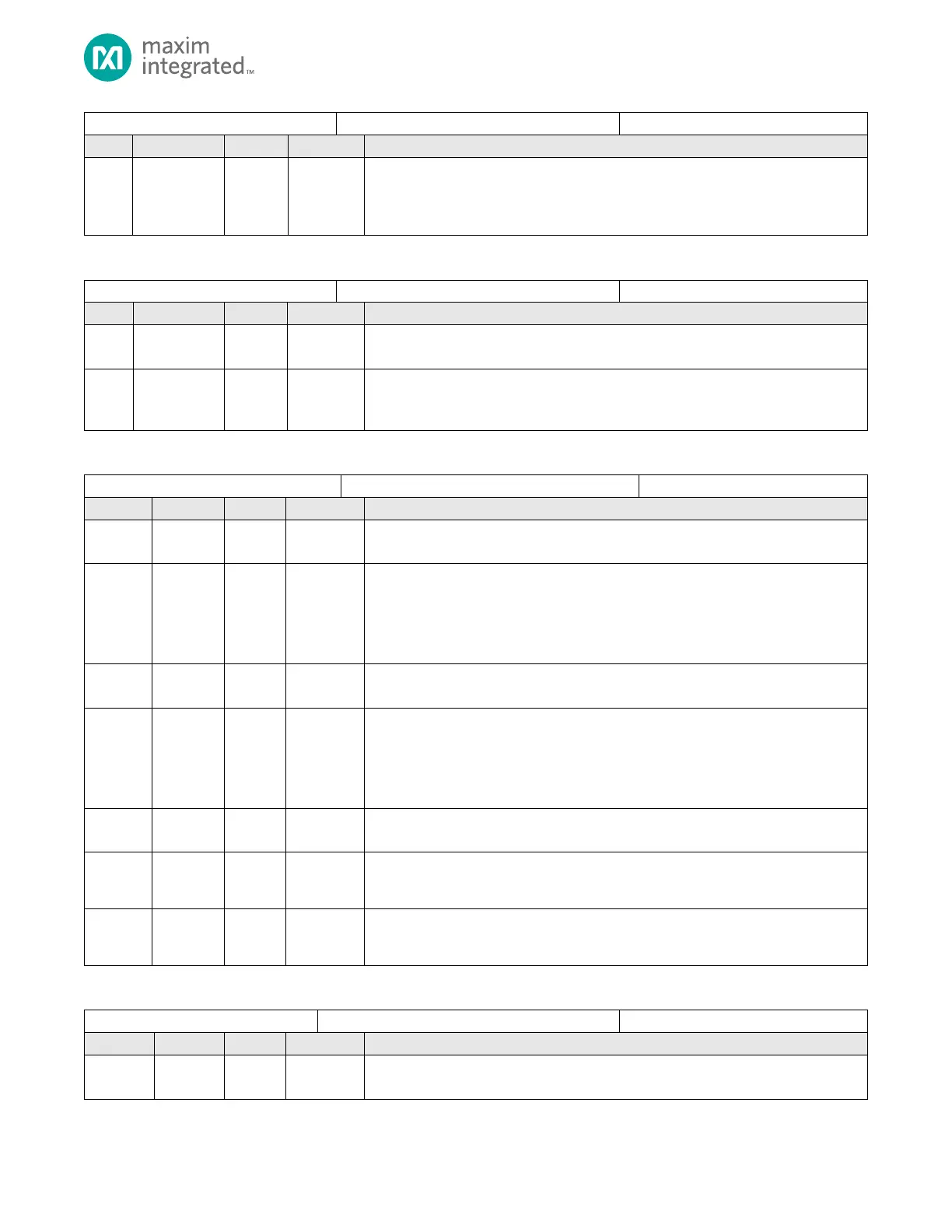

UART Baud Rate Decimal Register

Decimal Portion of Baud Rate Divisor

This field contains the remainder portion of the bit rate divisor. Refer to the UART Bit

Rate Calculation

bit rate.

Table 8-10: UART FIFO Register

Reserved for Future Use

Do not modify this field.

UART FIFO Register

Reading this field reads data from the RX FIFO and writes to this field write to the TX

FIFO.

Table 8-11: UART DMA Configuration Register

UART DMA Configuration Register

Reserved for Future Use

Do not modify this field.

RX FIFO Level DMA Trigger

If the RX FIFO level is greater than this value, the DMA channel transfers data from the

RX FIFO into memory. DMA transfers continue until the RX FIFO is empty. To avoid an

RX FIFO overrun, do not set this value to 32.

Values above 32 are reserved for future use.

Reserved for Future Use

Do not modify this field.

TX FIFO Level DMA Trigger

If the TX FIFO level is less than this value, the DMA channel transfers data from

memory into the TX FIFO. DMA transfers continue until the TX FIFO is full. To avoid

stalling a UART transmission, do not set this value to 1 or 0.

Values above 32 are reserved for future use.

Reserved for Future Use

Do not modify this field.

RX FIFO DMA Channel Enable

0: RX DMA is disabled

1: RX DMA is enabled

TX FIFO DMA Channel Enable

0: TX DMA is disabled

1: TX DMA is enabled

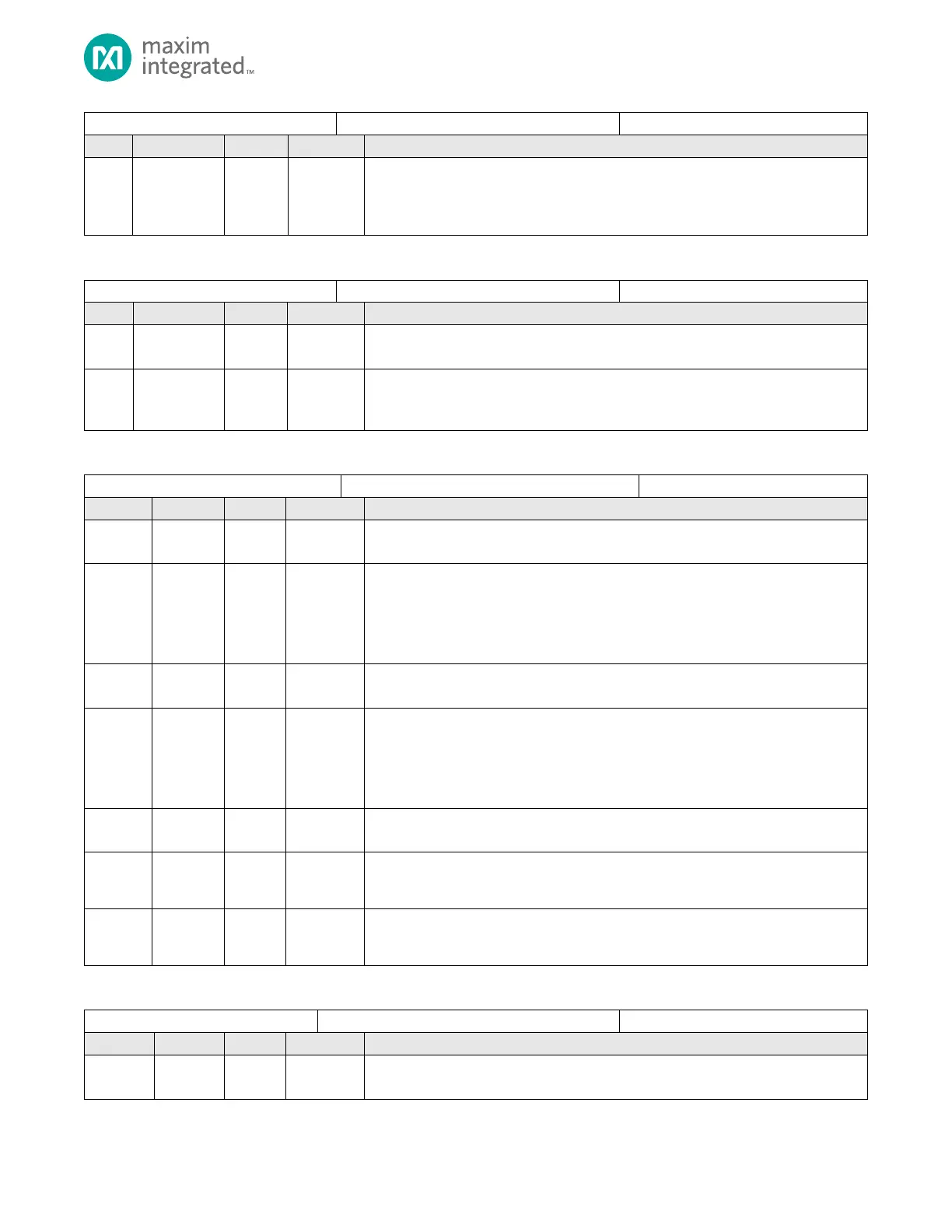

Table 8-12: UART TX FIFO Data Output Register

UART TX FIFO Data Output Register

Reserved for Future Use

Do not modify this field.

Loading...

Loading...