MAX32660 User Guide

Maxim Integrated Page 66 of 195

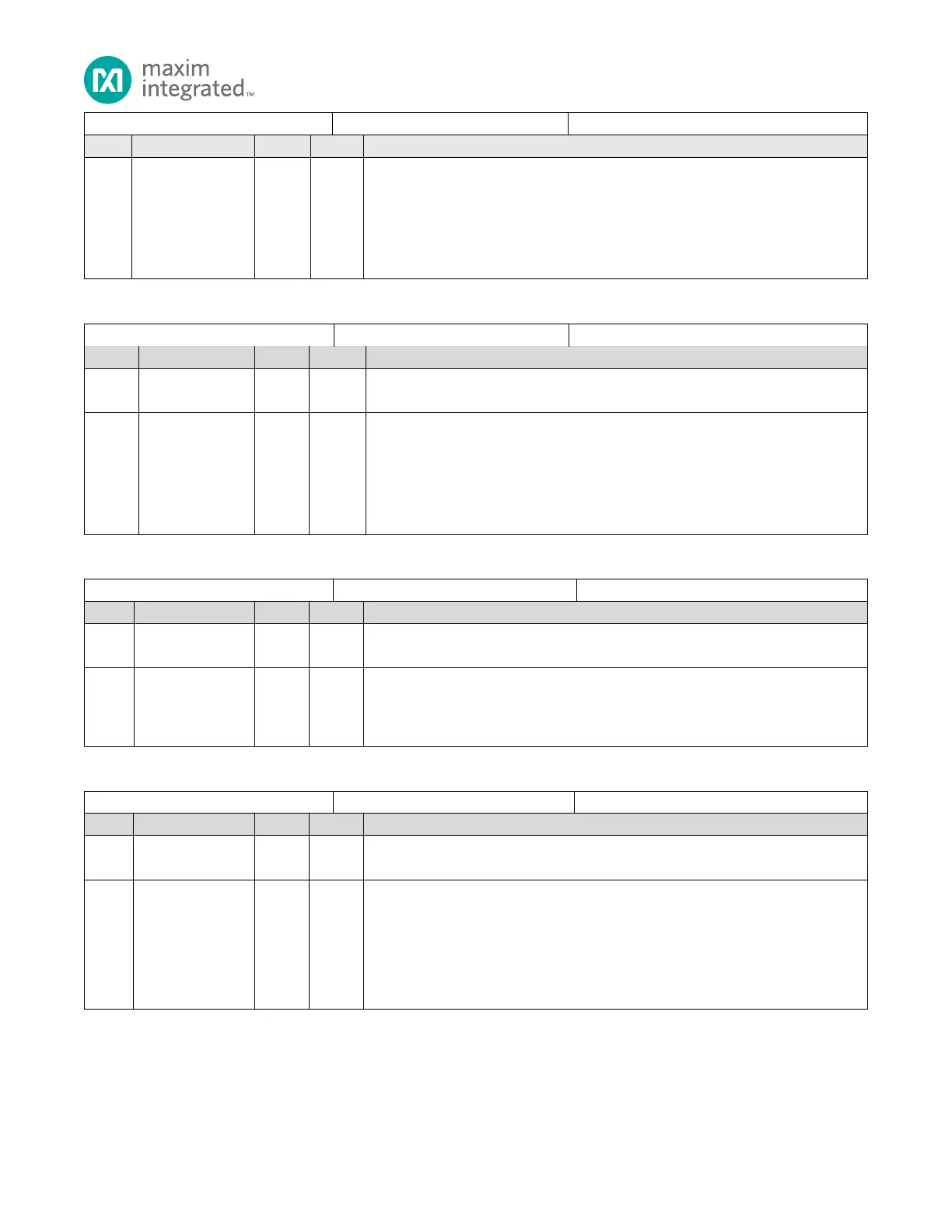

GPIO Interrupt Enable Register

GPIO Interrupt Enable

Enable or Disable the interrupt for the corresponding GPIO pin.

0: GPIO interrupt disabled.

1: GPIO interrupt enabled.

Note: Disabling a GPIO interrupt does not clear pending interrupts for the associated

pin. Use the GPIO0_INT_CLR register to clear pending interrupts.

Table 6-16: GPIO Interrupt Flag Register

GPIO Interrupt Flag Register

Reserved for Future Use

Do not modify this field.

GPIO Interrupt Status

An interrupt is pending for the associated GPIO pin when this bit reads 1.

0: No interrupt pending for associated GPIO pin.

1: GPIO interrupt pending for associated GPIO pin.

Note: Write a 1 to the corresponding bit in the GPIO0_INT_CLR register to clear the

interrupt pending status flag.

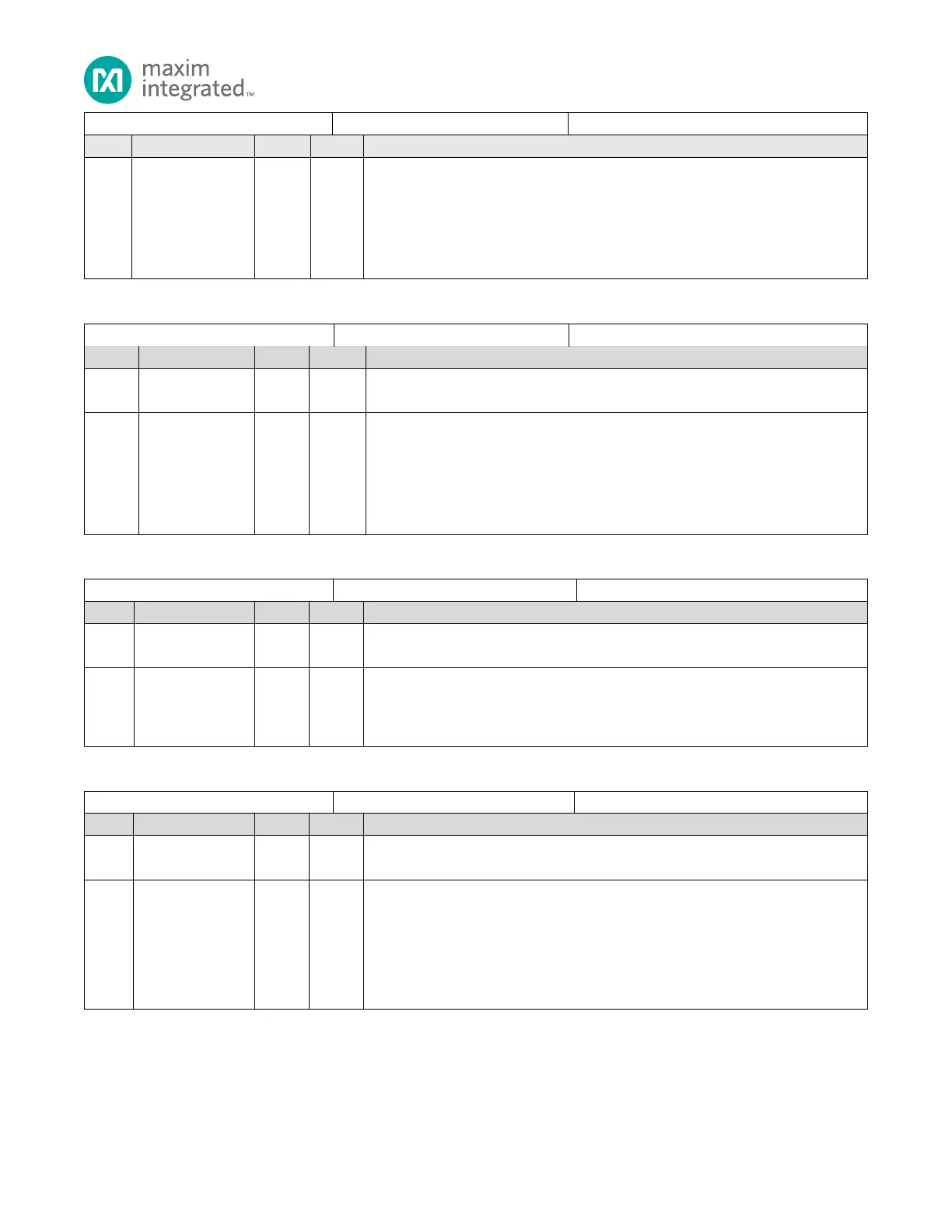

Table 6-17: GPIO Wakeup Enable Registers

GPIO Wakeup Enable Register

Reserved for Future Use

Do not modify this field.

GPIO Wakeup Enable

Enable the I/O as a wakeup from low power modes (SLEEP, DEEPSLEEP, BACKUP).

0: GPIO is not enabled as a wakeup source from low power modes.

1: GPIO is enabled as a wakeup source from low power modes.

Table 6-18: GPIO Interrupt Dual Edge Mode Registers

GPIO Interrupt Dual Edge Mode Register

Reserved for Future Use

Do not modify this field.

GPIO Interrupt Dual-Edge Mode Select

Setting this bit selects dual edge mode triggered interrupts (rising and falling edge

triggered) if the associated GPIO0_INT_MODE bit is set to edge triggered. When dual

edge mode is set, and the interrupt mode is edge-triggered, the associated polarity

(GPIO0_INT_POL) setting has no effect.

0: Dual edge detection mode interrupts disabled.

1: Dual edge detection mode interrupts enabled.

Loading...

Loading...