MAX32660 User Guide

Maxim Integrated Page 93 of 195

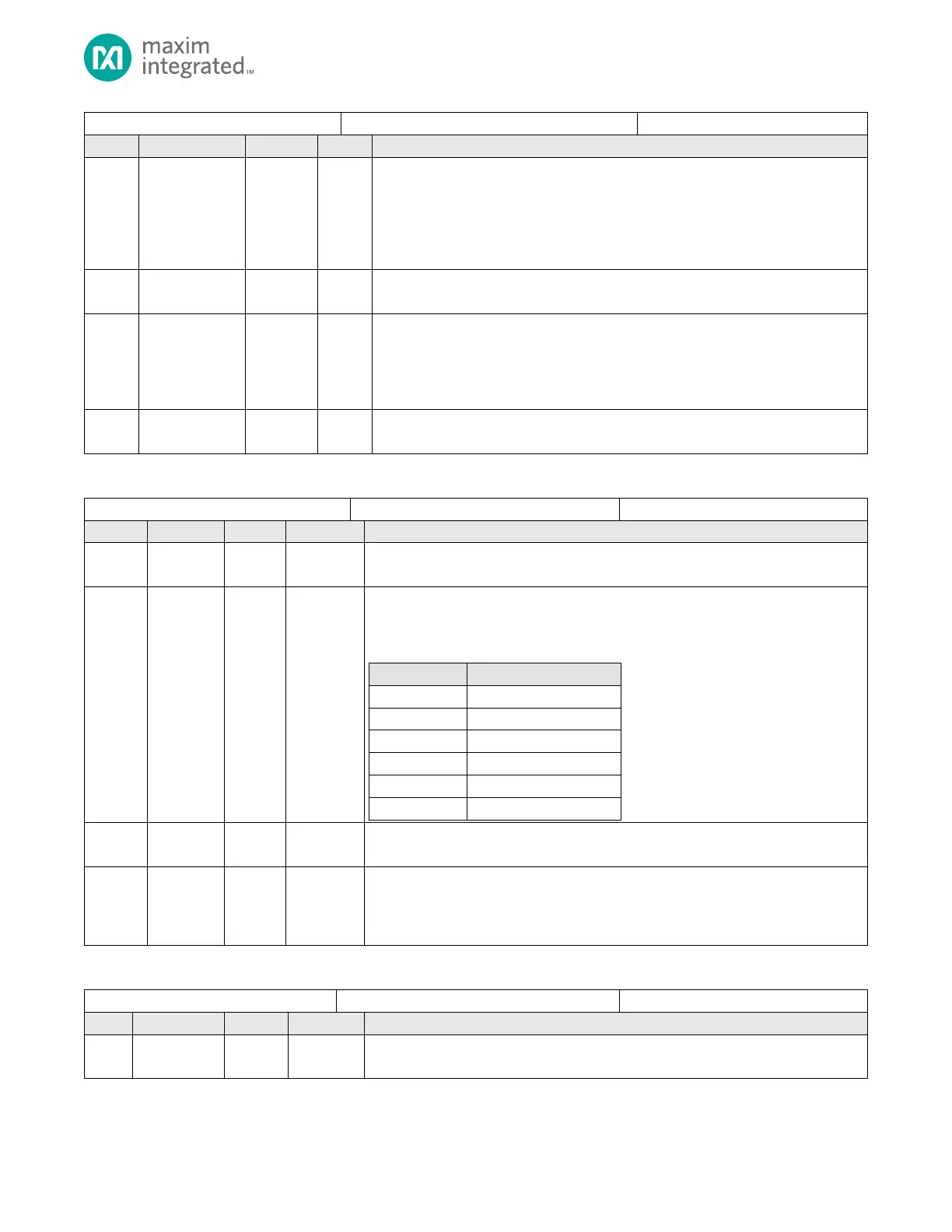

UART Interrupt Flags Register

RX FIFO Overrun Interrupt Flag

This field is set if the receive FIFO is full and an additional byte is received resulting in

a FIFO overrun condition. If this field is set at least one byte of received data has

been lost. Write 1 to clear.

0: RX FIFO overrun has not occurred.

1: RX FIFO overrun occurred.

CTS Interrupt Flag

CTS, also referred to as Modem Status Interrupt, flag. Write 1 to clear.

Receive Parity Error Status Flag

Set if a parity error is detected. This flag applies to data received only. Write 1 to

clear.

0: Parity error has not been detected.

1: Parity error detected.

Frame Error Status Flag

Set if a frame error occurs while receiving data. Write 1 to clear.

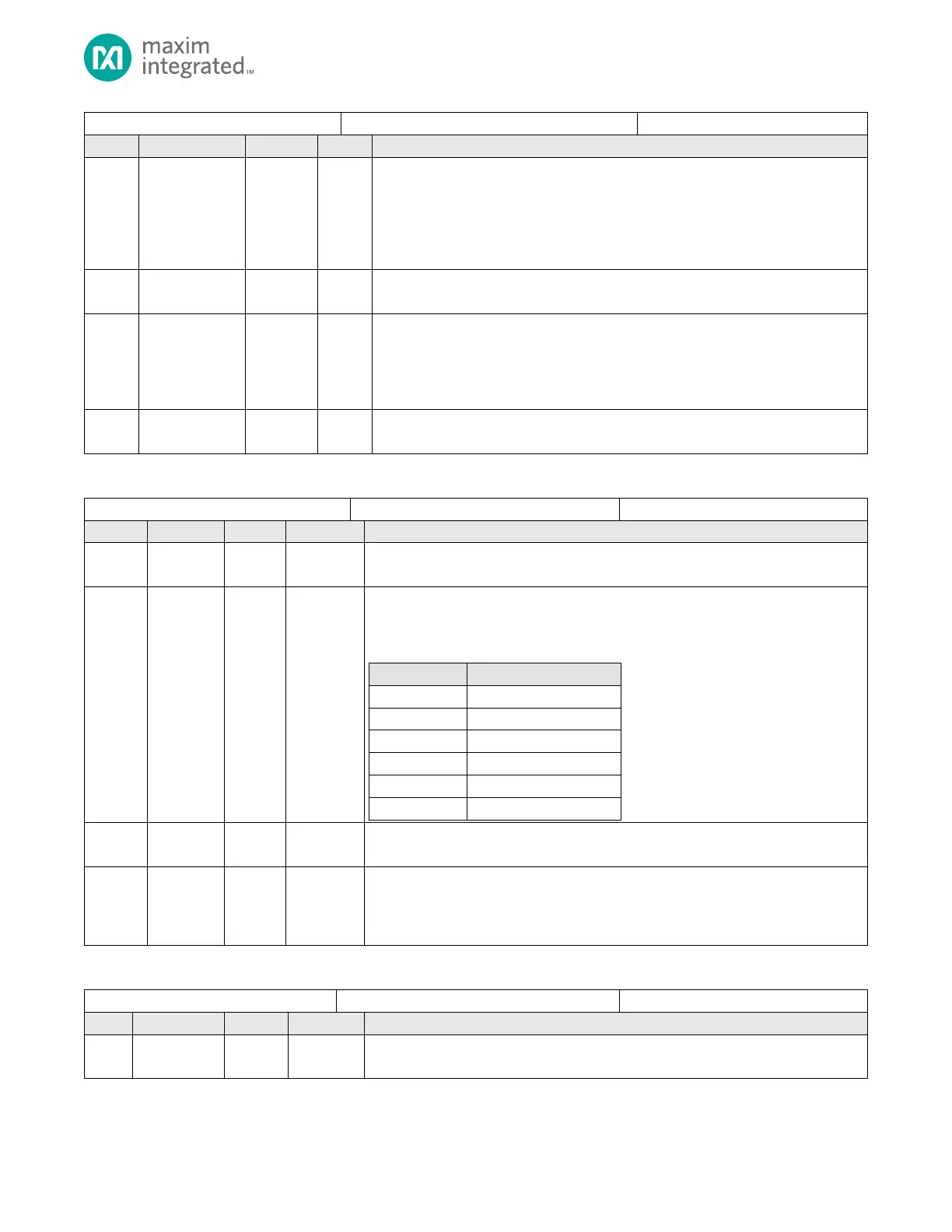

Table 8-8: UART Rate Integer Register

UART Baud Rate Integer Register

Reserved for Future Use

Do not modify this field.

Bit Rate Clock Divisor

This field is used to divide the bit rate clock by the selected Clock Divider value. Refer

to the UART Bit Rate Calculation

a given UART bit rate.

Reserved for Future Use

Do not modify this field.

Integer Portion of Baud Rate Divisor

This field contains the integer value of the bit rate divisor. Refer to the UART Bit Rate

Calculation section for d

rate.

Table 8-9: UART Baud Rate Decimal Register

UART Baud Rate Decimal Register

Reserved for Future Use

Do not modify this field.

Loading...

Loading...