MAX32660 User Guide

Maxim Integrated Page 24 of 195

4.2 System Clocks

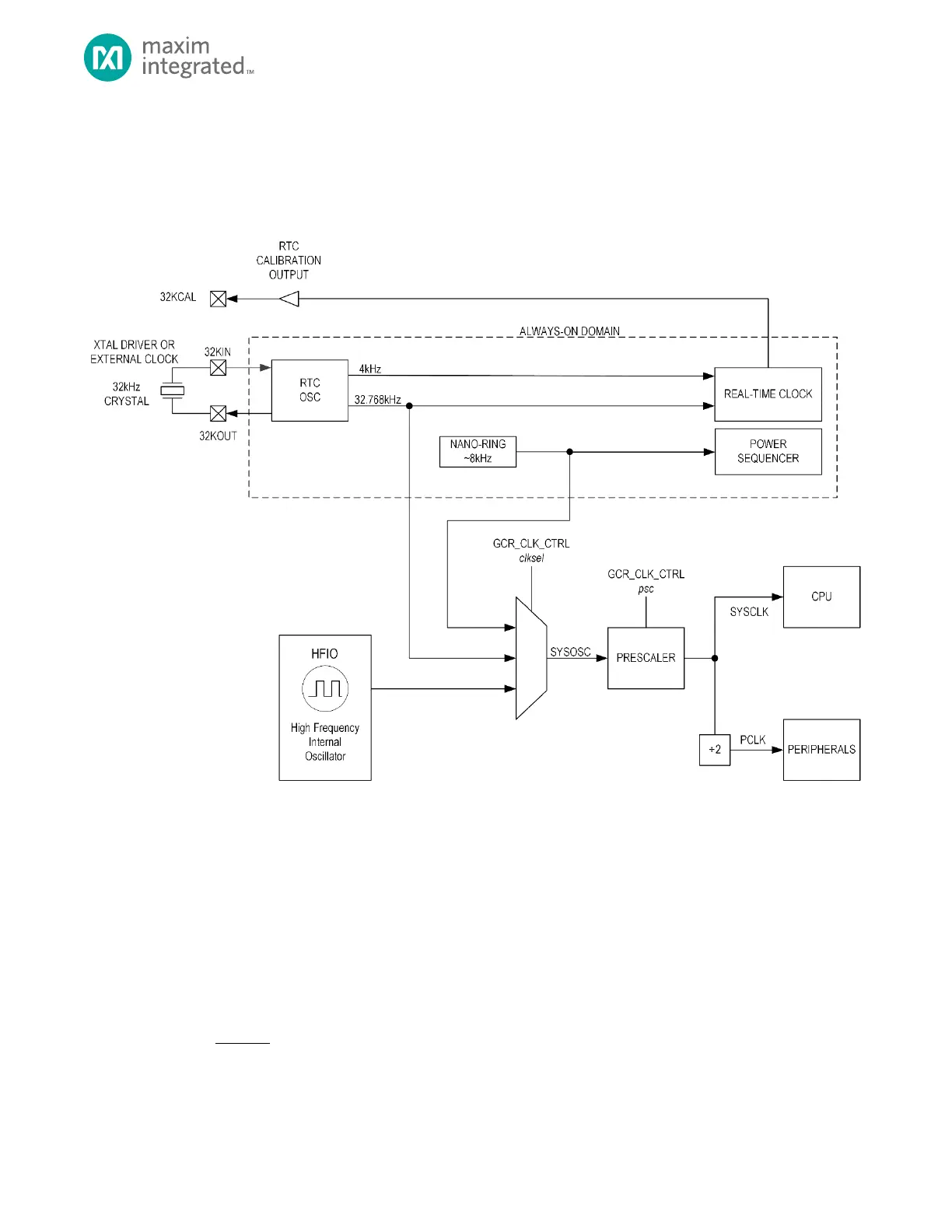

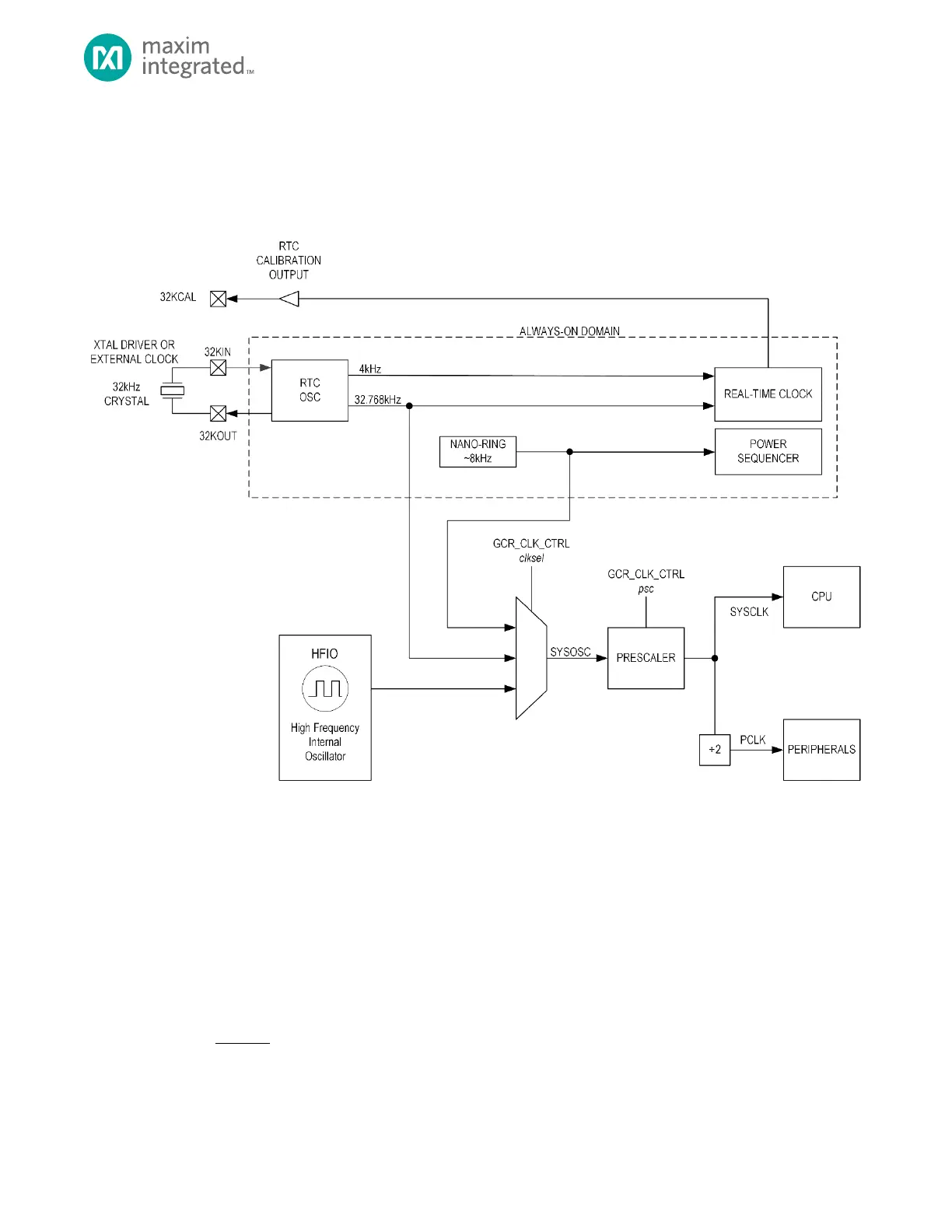

Figure 4-1, below, shows a high-level diagram of the MAX32660 clock tree.

Figure 4-1: Clock Tree Diagram

The selected System Oscillator (SYSOSC) is the clock source for most internal blocks. Select SYSOSC from the following clock

sources:

• High-Frequency Internal Oscillator (HFIO)

• 8kHz Internal Ultra-Low Power Nano-Ring Oscillator

• 32.768kHz External Crystal Oscillator

The selected SYSOSC is the input to the system oscillator prescaler, which generates the System Clock (SYSCLK). The system

oscillator prescaler divides SYSOSC by a prescaler using the GCR_CLK_CTRL.psc field as shown in Equation 4-1.

Equation 4-1: System Clock Scaling

GCR_CLK_CTRL.psc is selectable from 0 to 7, resulting in divisors of 1, 2, 4, 8, 16, 32, 64 or 128.

Loading...

Loading...