MAX32660 User Guide

Maxim Integrated Page 82 of 195

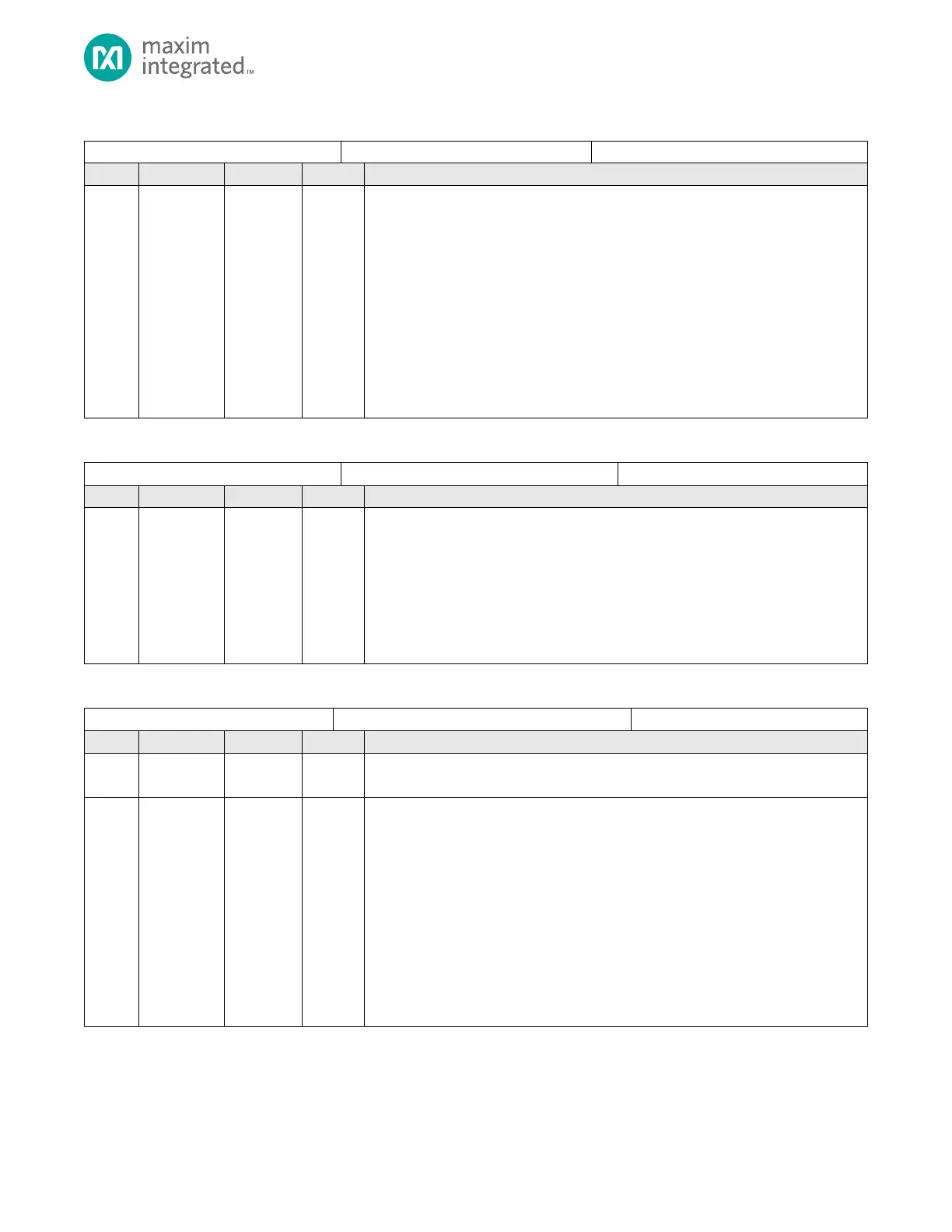

Table 7-13: DMA Source Register

Source Device Address

For peripheral transfers, the actual address field is either ignored or forced to zero

because peripherals only have one location to read/write data based on the request

select chosen.

If DMAn_CFG.srcinc = 1:

• This register is incremented on each AHB transfer cycle by one, two, or four bytes

depending on the data width.

If DMAn_CFG.srcinc = 0:

• This register remains constant.

If a CTZ condition occurs while DMAn_CFG.rlden = 1, then this register is reloaded

with the contents of the DMAn_SRC_RLD register.

Table 7-14: DMA Destination Register

Destination Device Address

For peripheral transfers, the actual address field is either ignored or forced to zero

because peripherals only have one location to read/write data based on the request

select chosen.

If DMAn_CFG.dstinc = 1, then this register is incremented on every AHB transfer cycle

by one, two, or four bytes depending on the data width.

If a CTZ condition occurs while DMAn_CFG.rlden = 1, then this register is reloaded

with the contents of the DMAn_DST_RLD register.

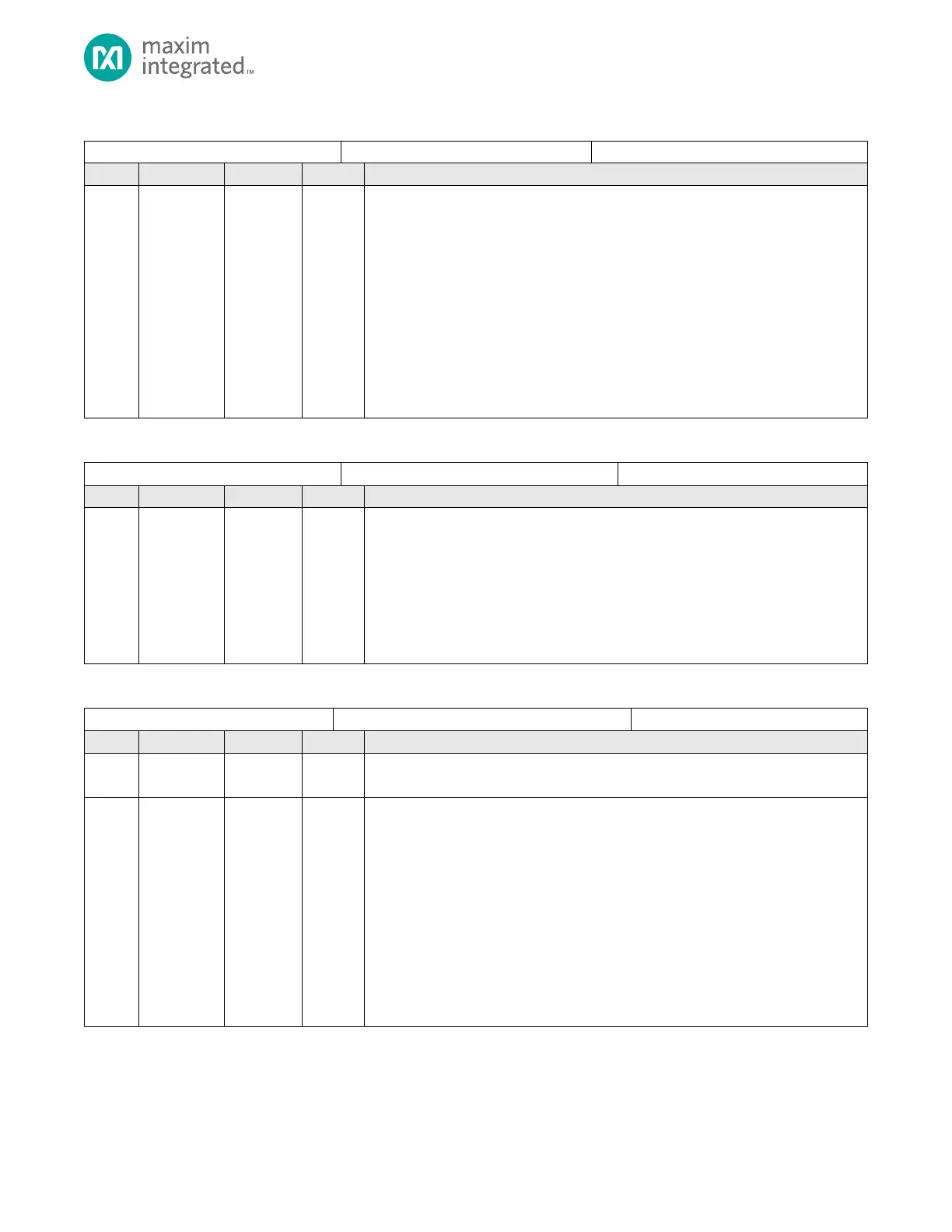

Table 7-15: DMA Count Register

Reserved for Future Use

Do not modify this field.

DMA Counter

Load this register with the number of bytes to transfer.

This counter decreases on every AHB access to DMA FIFO. The decrement is one, two,

or four bytes depending on the data width.

When the counter reaches 0, a CTZ condition is triggered.

If a CTZ condition occurs while DMAn_CFG.rlden = 1, then this register is reloaded with

the contents of the DMAn_CNT_RLD register.

0x000000: 0 Byte

0x000001: 1 Byte

0x000002: 2 Bytes

0xFFFFFF:16,777,215 Bytes

Loading...

Loading...