MAX32660 User Guide

Maxim Integrated Page 79 of 195

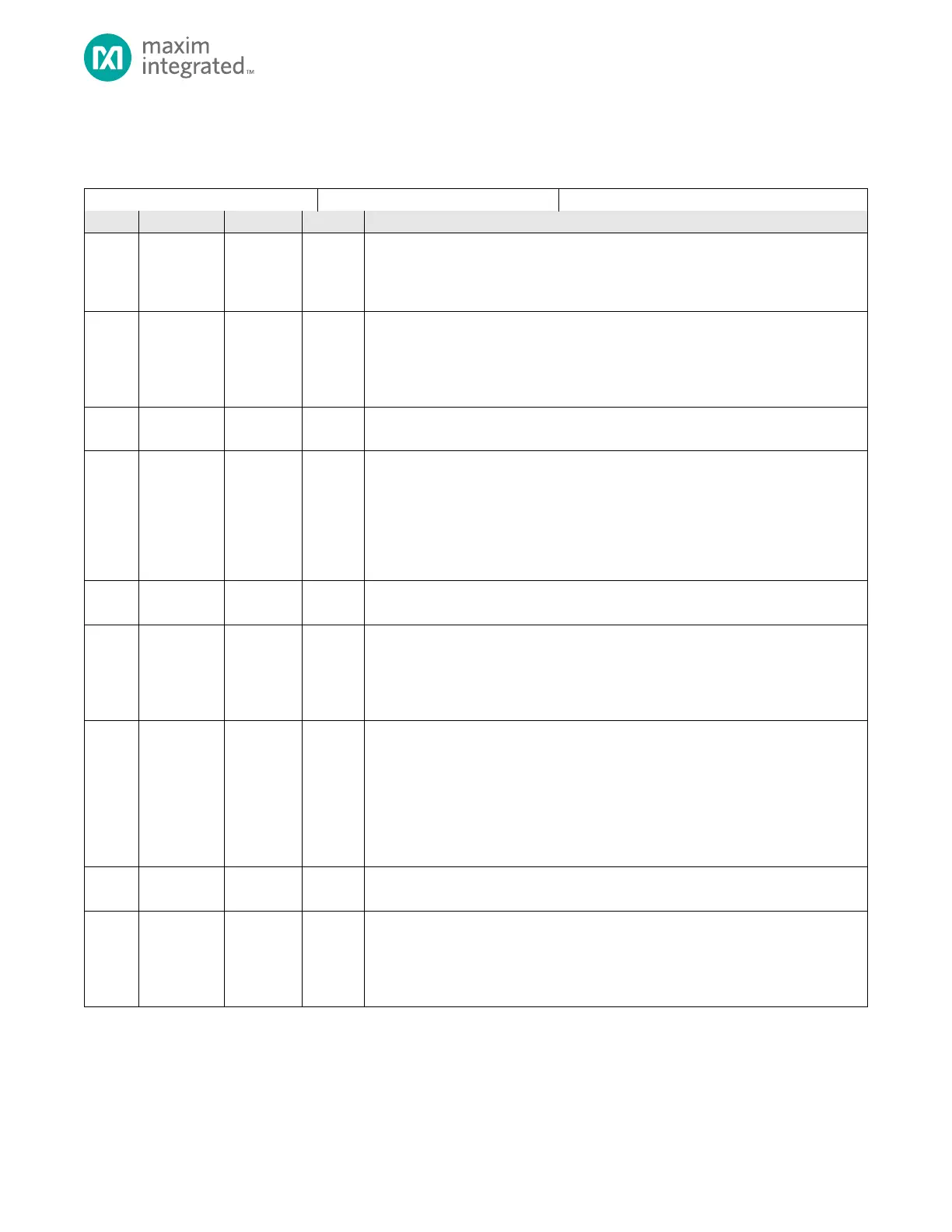

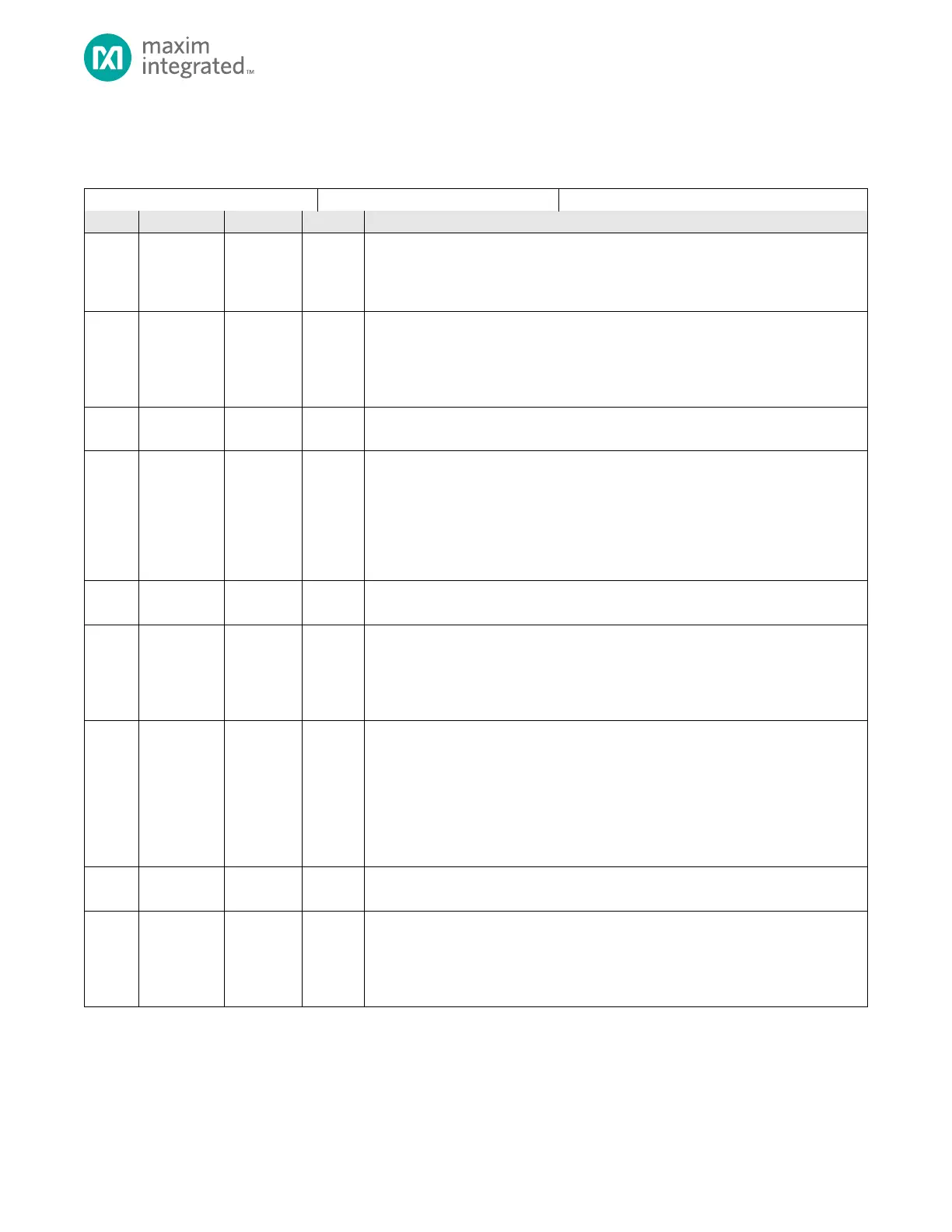

7.15.1 Standard DMA Channel Configuration Register Details

Table 7-11: DMA Configuration Register

DMA Configuration Register

CTZ Interrupt Enable

When enabled, the DMA_INT_FL.ipend bit is set to 1 whenever a CTZ event occurs.

0: Interrupt disabled

1: Interrupt enabled

Channel Disable Interrupt Enable

When enabled, the DMA_INT_FL.ipend bit is set to 1 whenever the DMAn_STAT.ch_st

bit changes from 1 to 0.

0: Interrupt disabled

1: Interrupt enabled

Reserved for Future Use

Do not modify this field.

Burst Size

The number of bytes transferred into and out of the DMA FIFO in a single burst.

0b00000: 1 byte

0b00001: 2 bytes

0b00010: 3 bytes

...

0b11111: 32 bytes

Reserved for Future Use

Do not modify this field.

Destination Increment Enable

This bit enables the automatic increment of the DMAn_DST register upon every AHB

transaction. This bit is forced to 0 for a DMA transmit to peripherals.

0: Increment disabled

1: Increment enabled

Destination Width

Indicates the width of each AHB transaction to the destination peripheral or memory

(the actual width might be less than this if there are insufficient bytes in the DMA FIFO

for the full width).

0b00: Byte

0b01: Two bytes

0b10: Four bytes

0b11: Reserved (Byte width if set)

Reserved for Future Use

Do not modify this field.

Source Increment Enable

This bit enables the automatic increment of the DMAn_SRC register upon every AHB

transaction. This bit is forced to 0 for a DMA receive from peripherals.

0: Increment disabled

1: Increment enabled

Loading...

Loading...