MAX32660 User Guide

Maxim Integrated Page 80 of 195

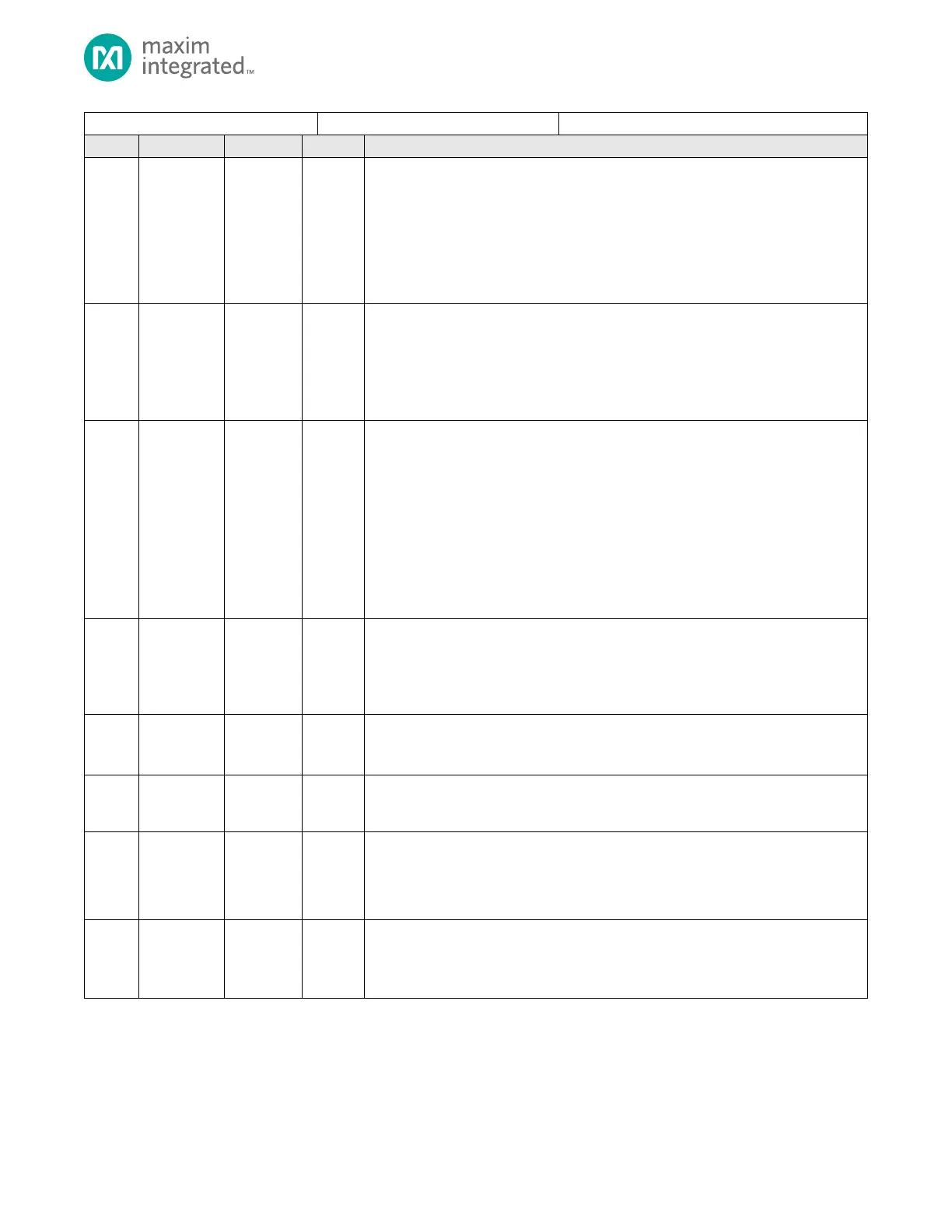

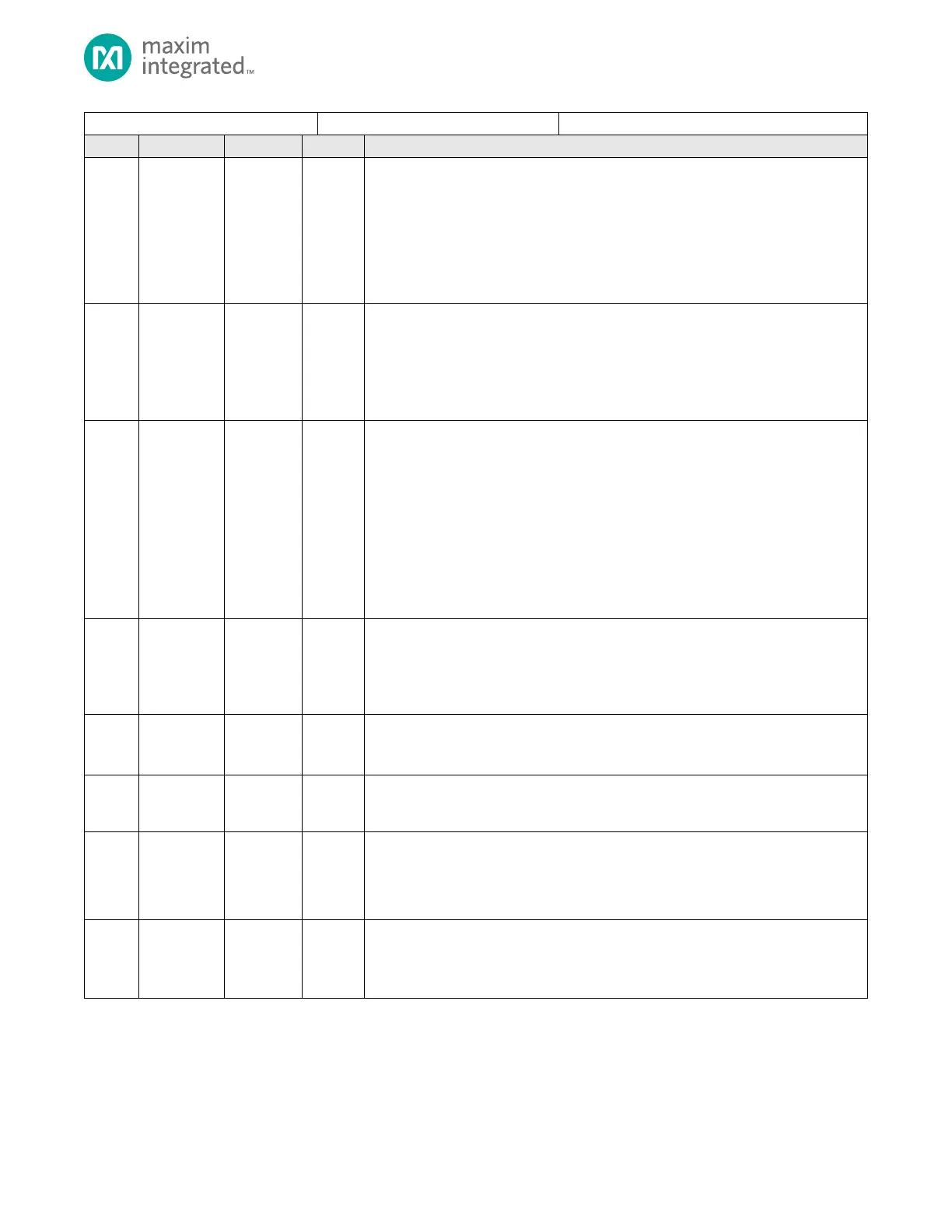

DMA Configuration Register

Source Width

Indicates the width of each AHB transaction from the source peripheral or memory.

The actual width might be less than this if the DMAn_CNT register indicates a smaller

value.

00: Byte

01: Two bytes

10: Four bytes

11: Reserved (byte width if set)

Pre-Scale Select

Selects the divider for -bit timer.

00: Disable timer

01:

10:

11:

Time-Out Select

Selects the number of prescaler clocks seen by the channel timer before a time-out

condition is generated for this channel.

000: 3-4

001: 7-8

010: 15-16

011: 31-32

100: 63-64

101: 127-128

110: 255-256

111: 511-512

Request Wait Enable

When enabled, delay the timeout timer start until after the first DMA transaction

occurs.

0: Start timer normally

1: Delay timer start

Request Select

Select DMA request line for this channel. If memory to memory is selected, then the

channel operates as if the request is always active.

DMA priority

00: Highest priority

11: Lowest priority

Reload Enable

Setting this bit to 1 allows reloading the DMAn_SRC, DMAn_DST, and DMAn_CNT

registers with their corresponding reload registers upon CTZ.

Note: This bit is also writeable in the DMAn_CNT_RLD register.

Channel Enable

This bit is automatically cleared when DMAn_STAT.ch_st changes from 1 to 0.

0: Disable this channel

1: Enable this channel

Loading...

Loading...