MAX32660 User Guide

Maxim Integrated Page 54 of 195

5.3.6 Mass Erase

Mass erase clears the internal flash memory. This operation requires the JTAG debug port to be enabled to perform the

operation. If the JTAG debug port is not enabled a mass erase operation cannot be performed. Perform the following steps

to mass erase the internal flash:

1. Set FLC_CTRL.unlock to 0x2 to unlock the internal flash.

2. Read the FLC_CTRL.busy bit until it returns 0.

3. Set FLC_CTRL.erase_code to 0xAA for mass erase.

4. Set FLC_CTRL.mass_erase to 1 to start the mass erase operation.

5. The FLC_CTRL.busy bit is set by the Flash Controller while the mass erase is in progress and the

FLC_CTRL.mass_erase and FLC_CTRL.busy are cleared by the Flash Controller when the mass erase is complete.

6. FLC_INTR.done is set by the Flash Controller when the mass erase completes. If an error occurred, the

FLC_INTR.access_fail flag is set. These bits generate a Flash Controller IRQ if the interrupt enable bits are set.

Note: Mass erase requires the JTAG debug port to be enabled, if the JTAG debug port is disabled on the device an access fail

error is generated (FLC_INTR.access_fail = 1).

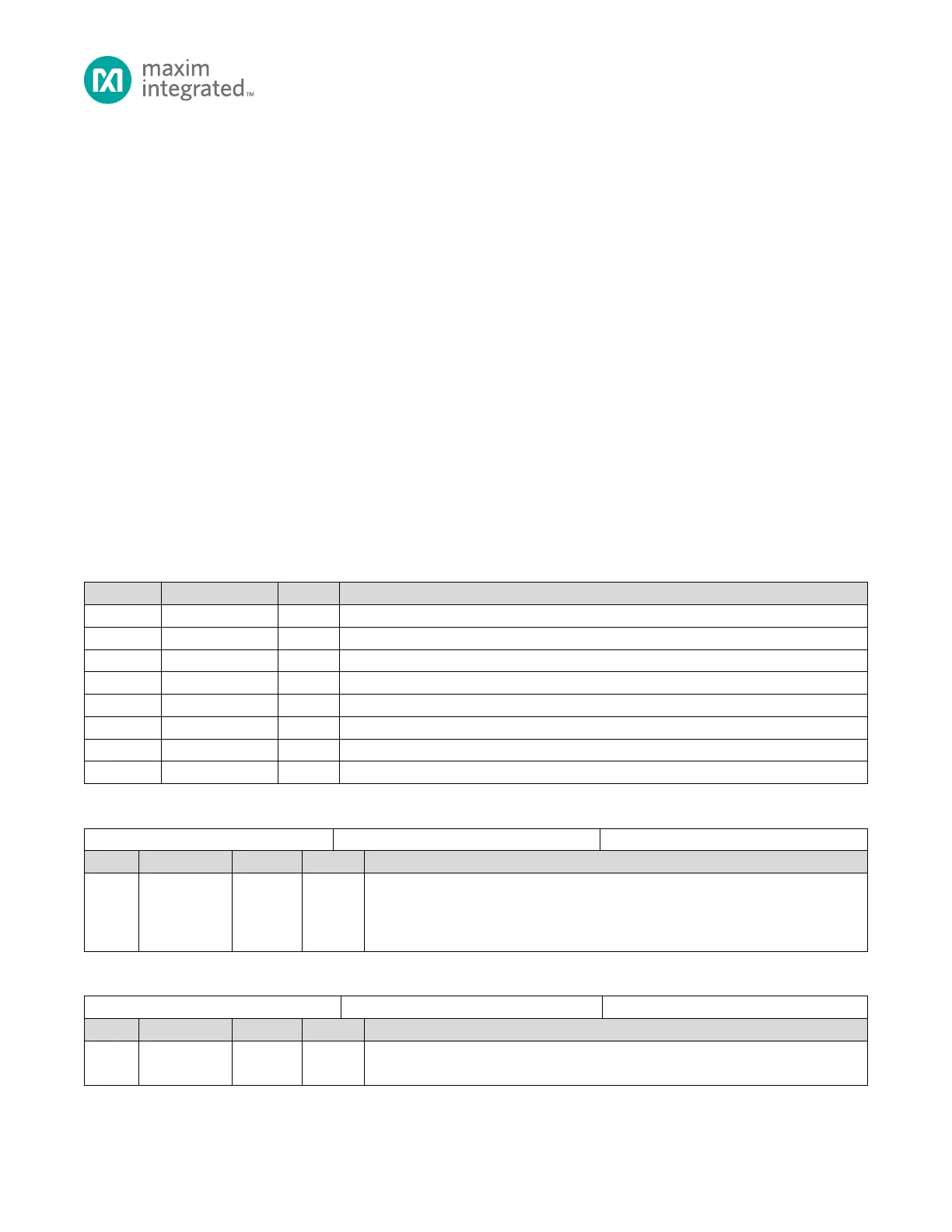

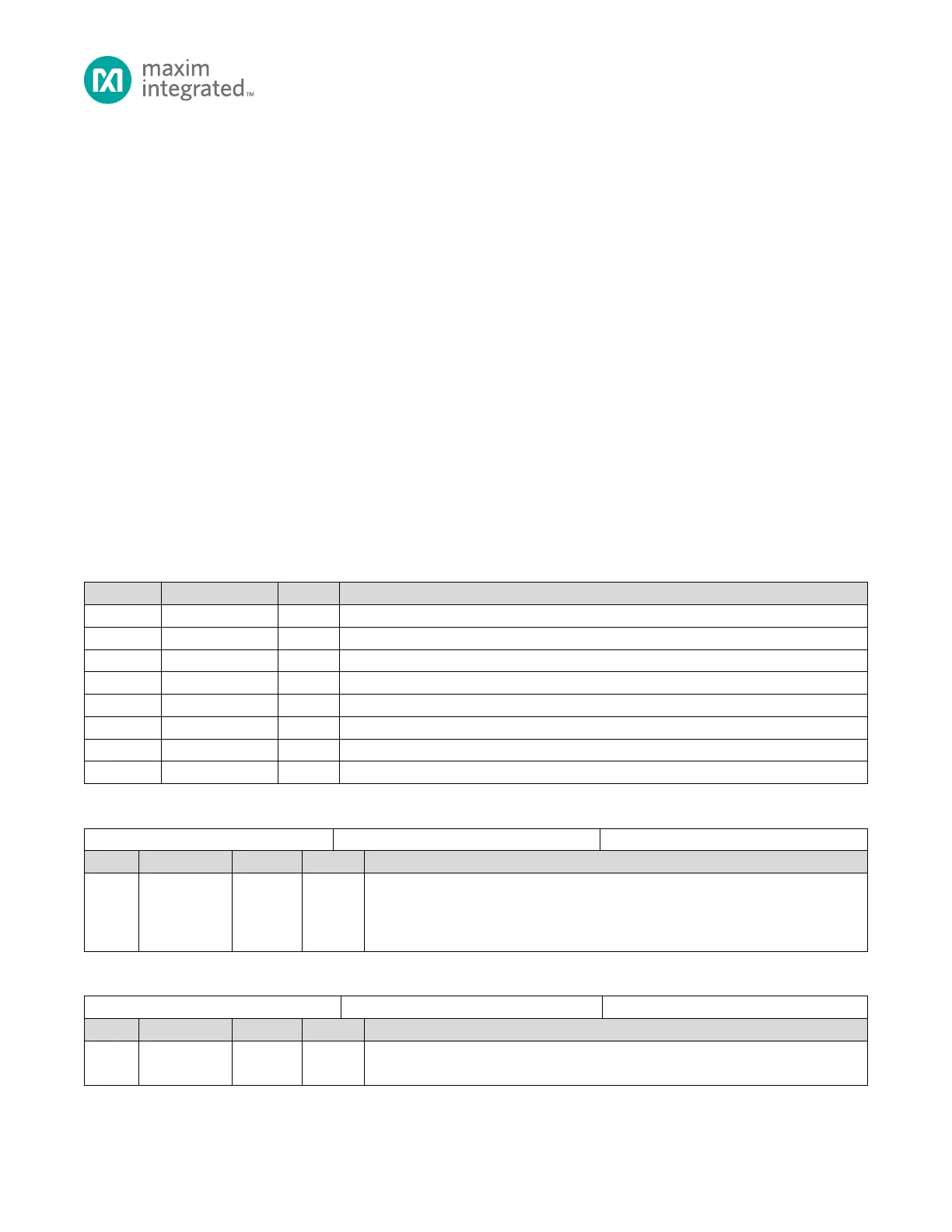

5.4 Flash Controller Registers

The FLC base peripheral address is 0x4002 9000. Refer to Table 3-1: APB Peripheral Base Address Map for the addresses of

all APB mapped peripherals.

Table 5-4: Flash Controller Registers, Offsets, Access and Descriptions

Loading...

Loading...