MAX32660 User Guide

Maxim Integrated Page 49 of 195

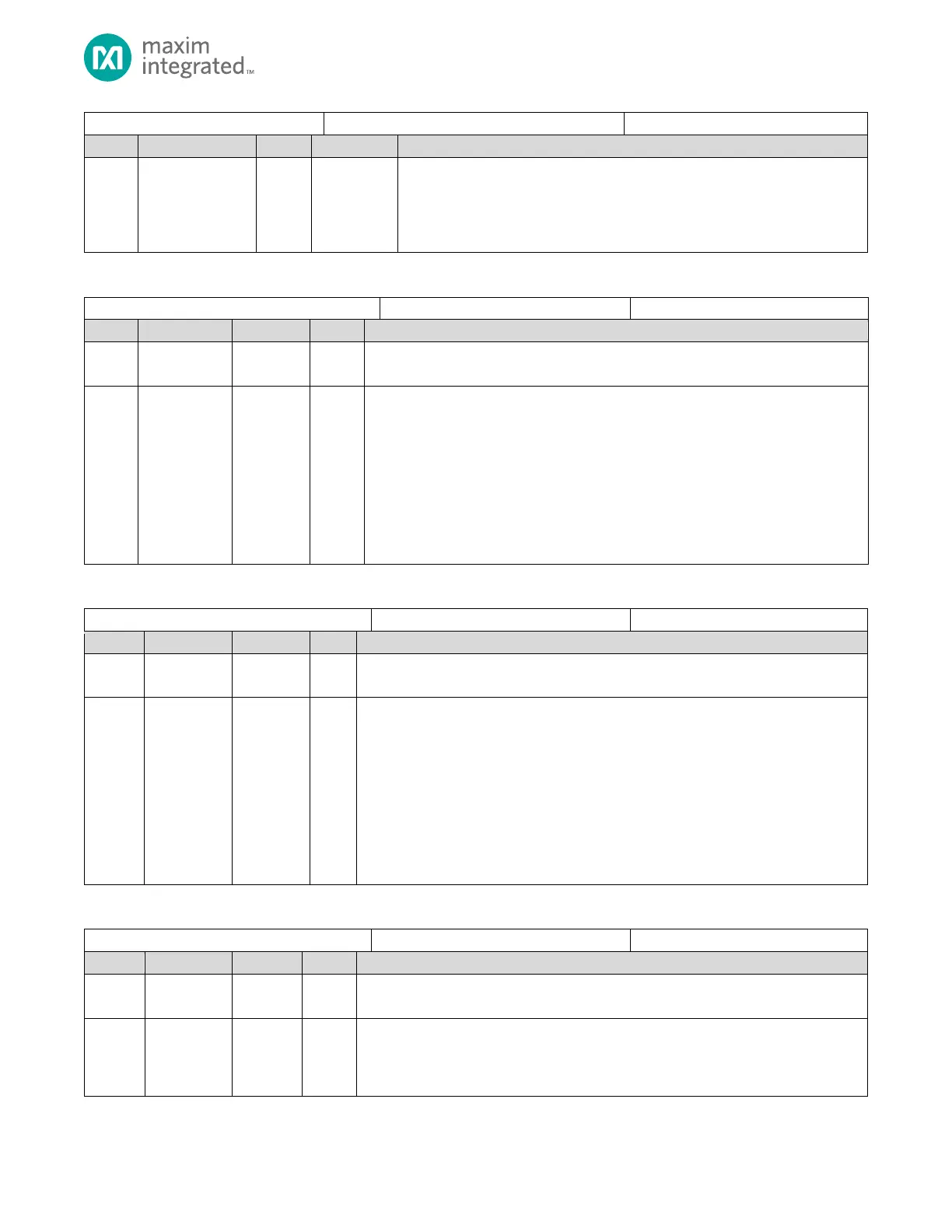

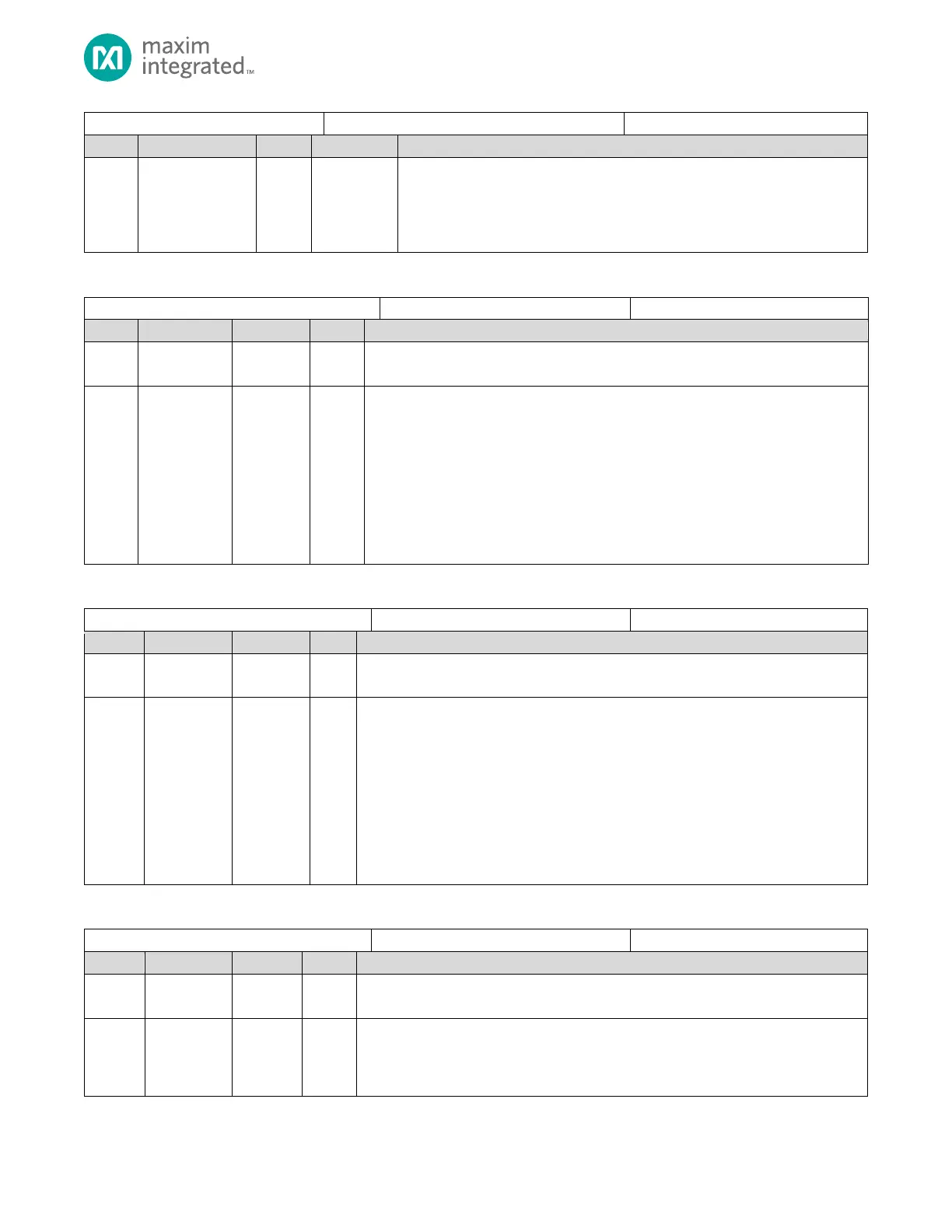

Low Power Voltage Control Register

System RAM 0 Data Retention Enable for BACKUP Mode

Set this field to 1 to enable Data Retention for System RAM 0, address range of

0x2000 0000 to 0x2000 3FFF.

0: Data retention for System RAM 0 address space disabled in BACKUP mode.

1: Data retention for System RAM 0 address space enabled in BACKUP mode.

Table 4-33: Low Power Mode Wakeup Flags for GPIO0

Low Power Mode GPIO Wakeup Flags Register

Reserved for Future Use

Do not modify this field.

GPIO Pin Wakeup Status Flag

When a GPIO pin transitions from low-to-high or high-to-low, the corresponding bit in

this field is set.

If the corresponding interrupt enable bit is set in PWRSEQ_LPWK_EN register and

GCR_PM.gpiowk_en bit is set to 1, a PWRSEQ IRQ is generated to wake up the device

from all low power modes to ACTIVE mode.

Note: To enable the device to wake up from a low power mode on a GPIO pin

transition, first set the GCR_PM GPIO wakeup enable field to 1

(GCR_PM.gpiowk_en = 1).

Table 4-34: Low Power Wakeup Enable for GPIO0 Register

Low Power Mode Wakeup Enable for GPIO0

Reserved for Future Use

Do not modify this field.

GPIO Pin Wakeup Interrupt Enable

Write 1 to a bit to enable the corresponding GPIO0 pin to generate a PWRSEQ IRQ to

wake up the device from any low power mode to ACTIVE mode. Set the

GCR_PM.gpiowk_en bit to 1 to enable GPIO wake up events.

A wake up occurs on any low-to-high or high-to-low transition on the corresponding

GPIO0 pin.

Note: To enable the device to wake up from a low power mode on a GPIO pin transition,

first set the global GPIO wakeup enable field, (GCR_PM.gpiowk_en = 1).

Table 4-35: RAM Shut Down Register

Low-Power Memory Shutdown Register

Reserved for Future Use

Do not modify this field.

System RAM 3 (0x2001 0000 - 0x2001 7FFF) Shut Down

Write 1 to shut down power to System RAM 3 memory range.

0: System RAM 3 Powered On (Enabled)

1: System RAM 3 Powered Off (Disabled)

Loading...

Loading...