MAX32660 User Guide

Maxim Integrated Page 48 of 195

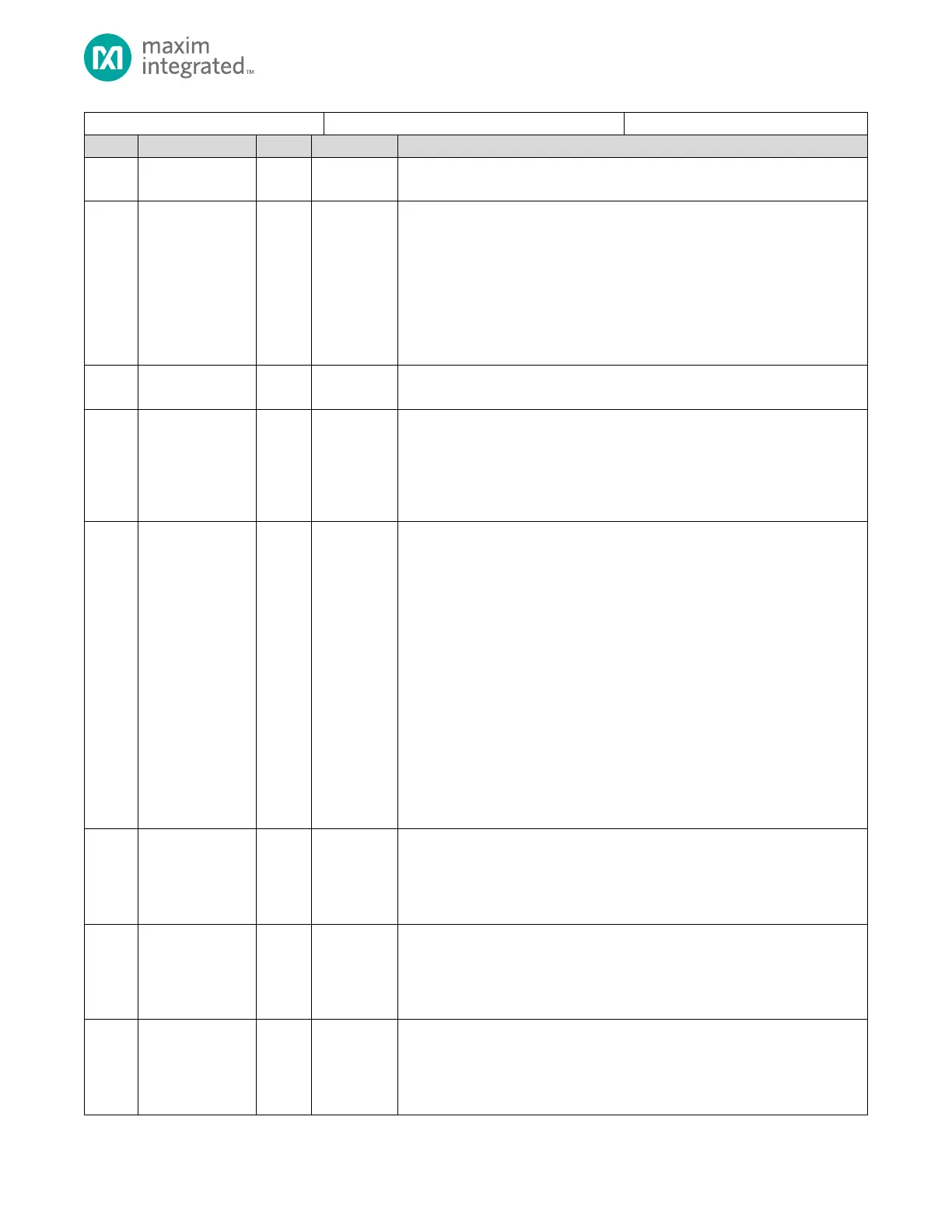

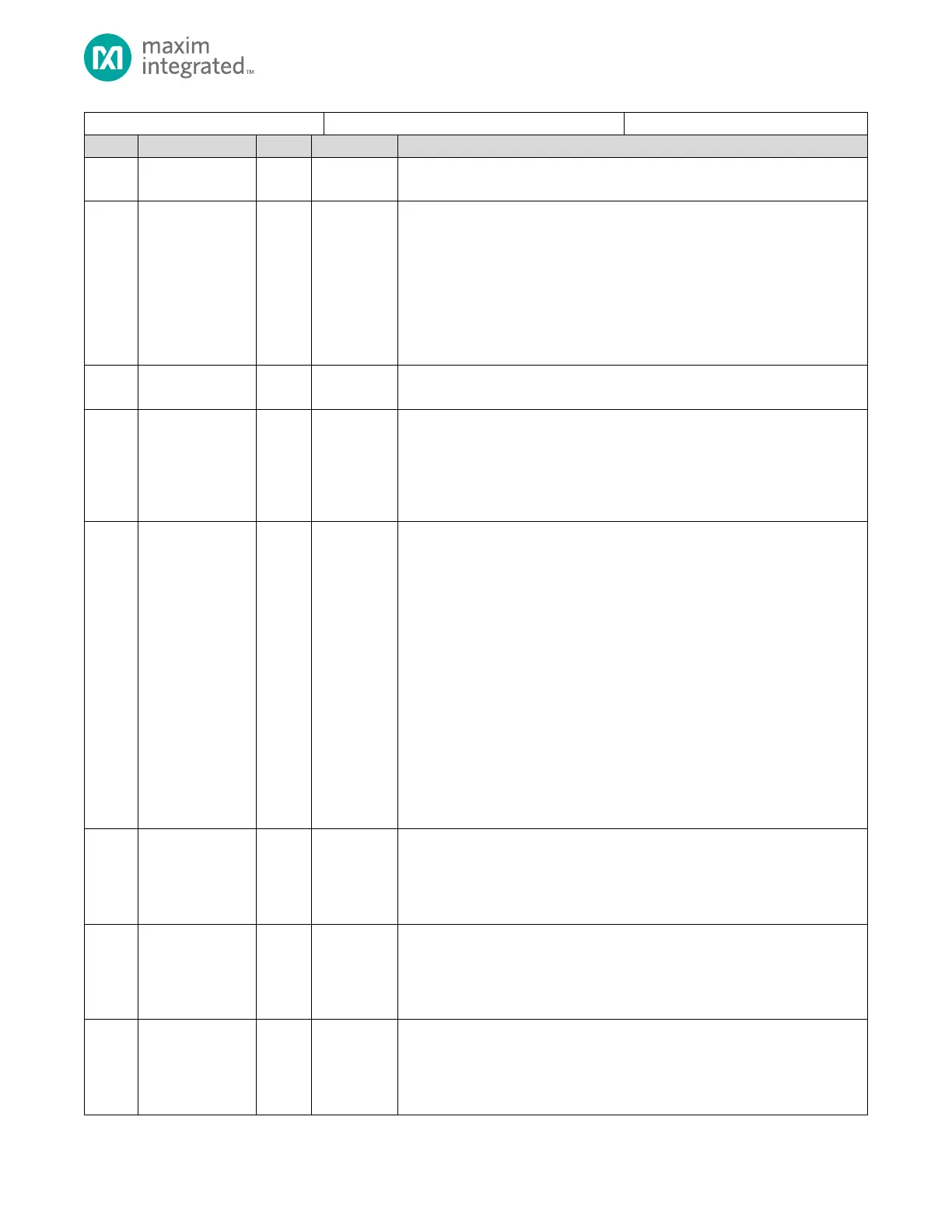

Low Power Voltage Control Register

Reserved for Future Use

Do not modify this field.

RAM Retention Regulator Enable for BACKUP Mode

This field selects the source used to retain the RAM contents during BACKUP

mode operation. Setting this field to 0 sets the V

DD

supply for RAM retention

during BACKUP mode and disables the RAM retention regulator.

0: RAM retention regulator disabled, the V

DD

supply is used to retain the state

of the internal SRAM as configured by the

PWRSEQ_LP_CTRL.ramret_sel[3:0] fields.

1: RAM retention regulator enabled. RAM retention in BACKUP mode is

configured with the PWRSEQ_LP_CTRL.ramret_sel[3:0] fields.

Reserved for Future Use

Do not modify this field.

Bypass V

CORE

External Supply Detection

Set this field to 1 if the system runs from a single supply only and V

CORE

is not

connected to an external supply. Bypassing the hardware detection of an

external supply on V

CORE

enables a faster wakeup time.

0: V

CORE

External Supply Detection Enabled.

1: V

CORE

External Supply Detection Disabled.

Output Voltage Range for Internal Regulator

Set these bits to control the output voltage of the internal regulator allowing

selection of the internal core operating voltage and the frequency of the internal

high frequency internal oscillator. On Power-On-Reset, this field defaults to 1.1V

output ± 10% with the

.

Note: If V

CORE

is connected to an external supply voltage, this field should be

modified only to set it to match the input voltage on V

CORE

.

Dual Supply Operation:

0b11: Reserved for Future Use

0b10: V

CORE

= 1.1V, f

INTCLK

=96MHz

0b01: V

CORE

= 1.0V, f

INTCLK

=48MHz

0b00: V

CORE

= 0.9V, f

INTCLK

=24MHz

Single Supply Operation (V

CORE

=GND)

0b11: Reserved for Future Use

0b10: V

LDO

= 1.1V, f

INTCLK

=96MHz

0b01: V

LDO

= 1.0V, f

INTCLK

=48MHz

0b00: V

LDO

= 0.9V, f

INTCLK

=24MHz

System RAM 3 Data Retention Enable for BACKUP Mode

Set this field to 1 to enable Data Retention for System RAM 3, address range of

0x2001 0000 to 0x2001 7FFF.

0: Data retention for System RAM 3 address space disabled in BACKUP mode.

1: Data retention for System RAM 3 address space enabled in BACKUP mode.

System RAM 2 Data Retention Enable for BACKUP Mode

Set this field to 1 to enable Data Retention for System RAM 2, address range of

0x2000 8000 to 0x2000 FFFF.

0: Data retention for System RAM 2 address space disabled in BACKUP mode.

1: Data retention for System RAM 2 address space enabled in BACKUP mode.

System RAM 1 Data Retention Enable for BACKUP Mode

Set this field to 1 to enable Data Retention for System RAM 1, address range of

0x2000 4000 to 0x2000 7FFF.

0: Data retention for System RAM 1 address space disabled in BACKUP mode.

1: Data retention for System RAM 1 address space enabled in BACKUP mode.

Loading...

Loading...