MAX32660 User Guide

Maxim Integrated Page 65 of 195

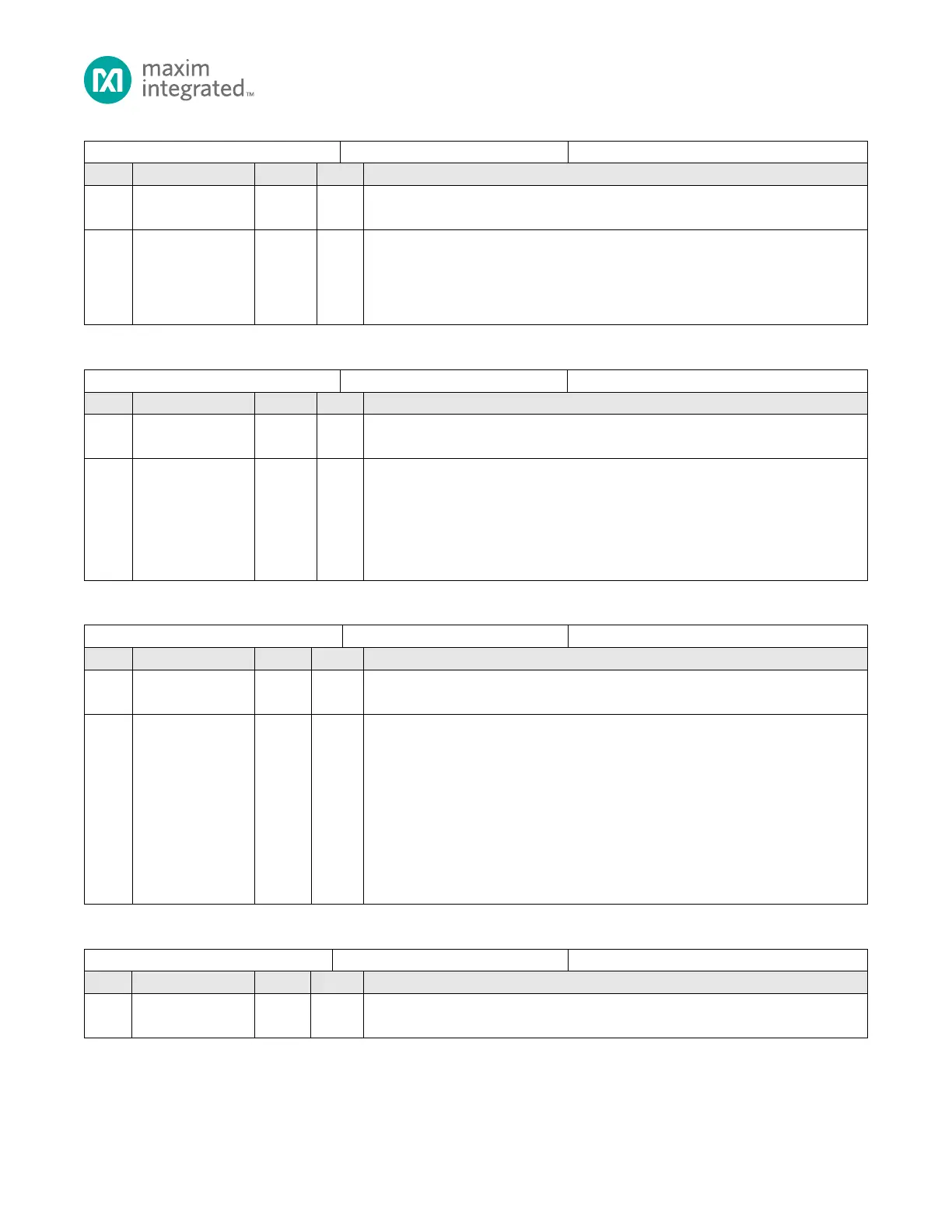

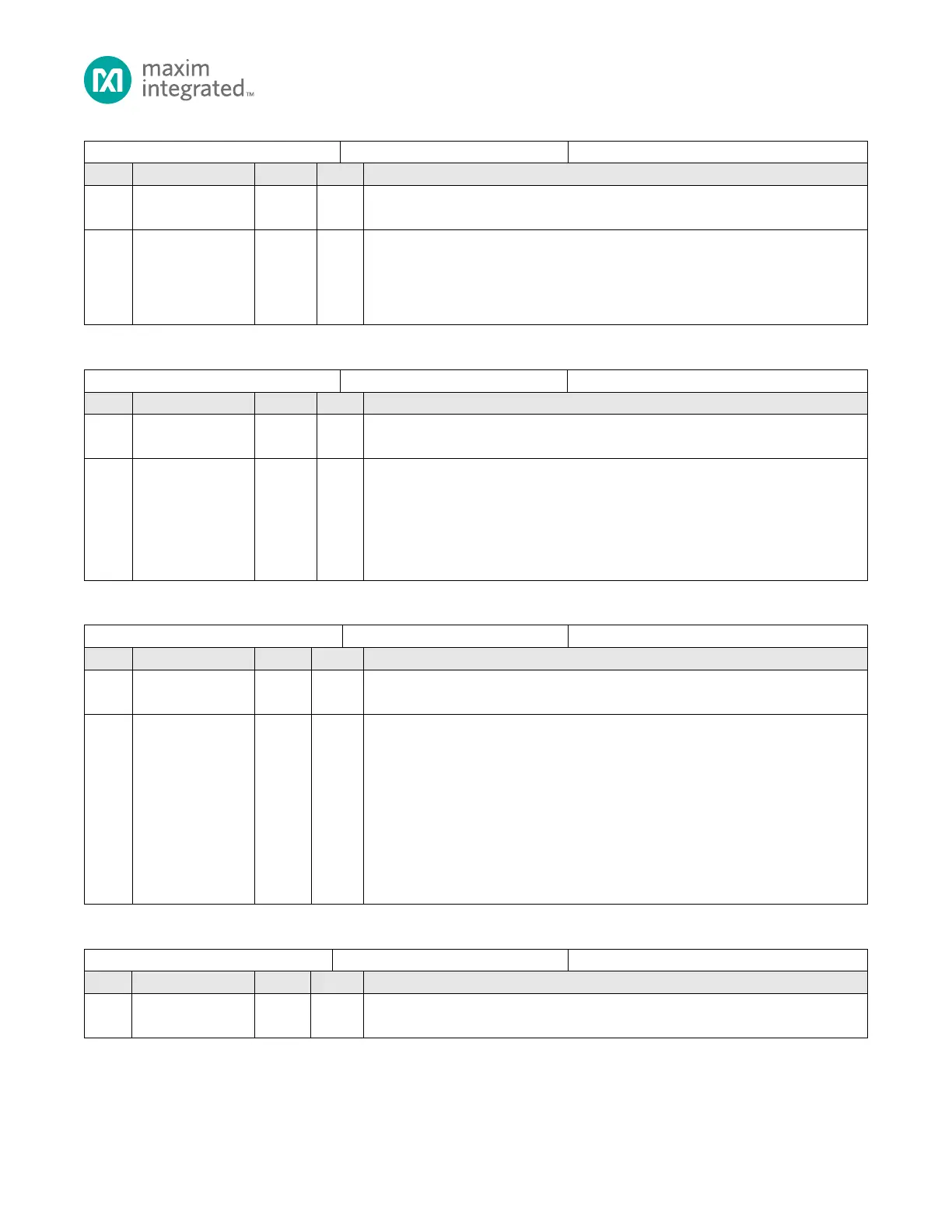

Table 6-12: GPIO Input Register

Reserved for Future Use

Do not modify this field.

GPIO Input Level

Read the state of the corresponding input pin. The input state is always readable for a

0: Input pin low (logic 0)

1: Input pin high (logic 1)

Table 6-13: GPIO Port Interrupt Mode Register

GPIO Port Interrupt Mode Register

Reserved for Future Use

Do not modify this field.

GPIO Interrupt Mode

Interrupt mode selection bit for the corresponding GPIO pin.

0: Level triggered interrupt for corresponding GPIO pin.

1: Edge triggered interrupt for corresponding GPIO pin.

Note: This bit has no effect unless the corresponding bit in the GPIO0_INT_EN register

is set.

Table 6-14: GPIO Port Interrupt Polarity Registers

GPIO Interrupt Polarity Register

Reserved for Future Use

Do not modify this field.

GPIO Interrupt Polarity

Interrupt polarity selection bit for the corresponding GPIO pin.

Level triggered mode (GPIO0_INT_MODE = 0):

0: Input low (logic 0) triggers interrupt.

1: Input high (logic 1) triggers interrupt.

Edge triggered mode (GPIO0_INT_MODE = 1):

0: Falling edge triggers interrupt

1: Rising edge triggers interrupt.

Note: This bit has no effect unless the corresponding bit in the GPIO0_INT_EN register

is set.

Table 6-15: GPIO Port Interrupt Enable Registers

GPIO Interrupt Enable Register

Reserved for Future Use

Do not modify this field.

Loading...

Loading...