MAX32660 User Guide

Maxim Integrated Page 56 of 195

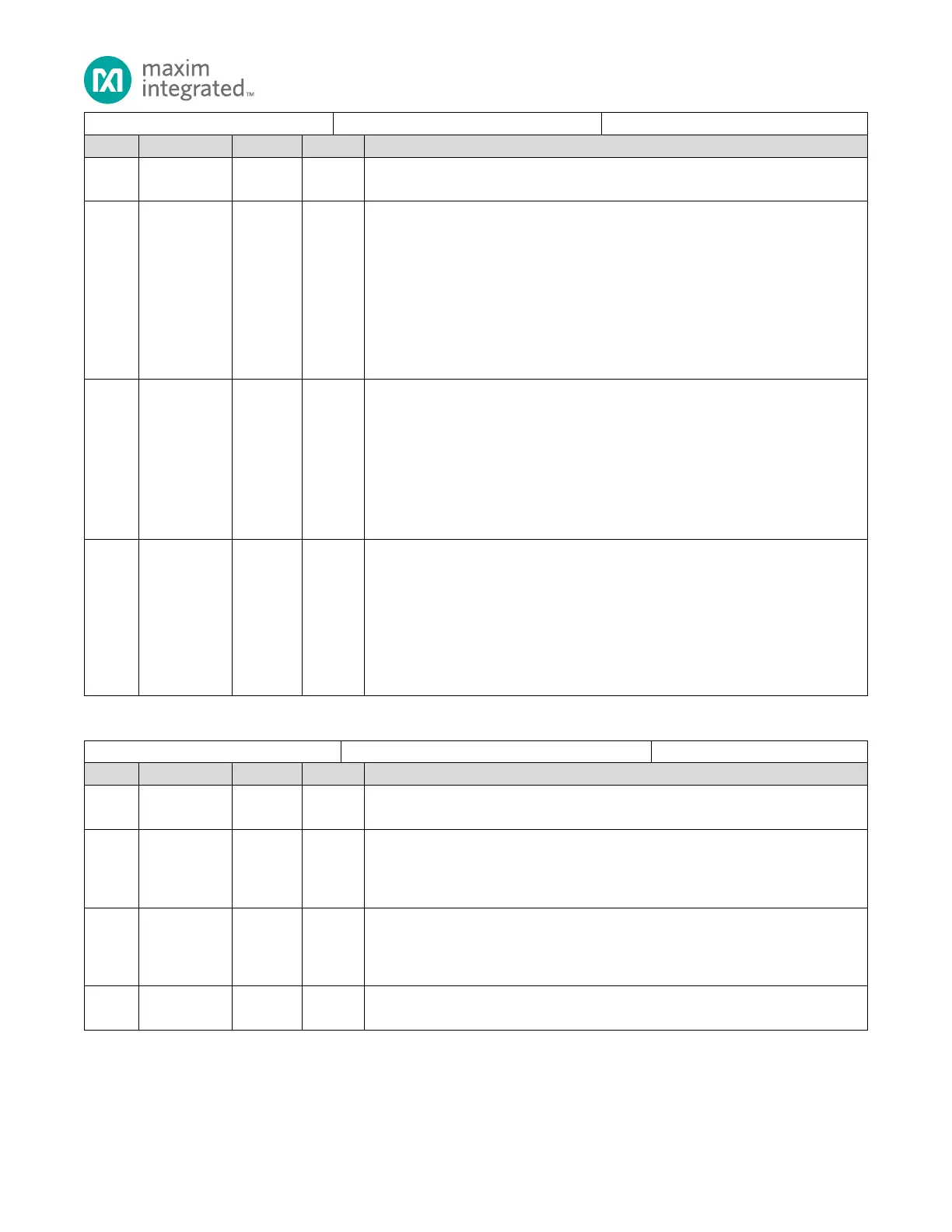

Flash Controller Control Register

Reserved for Future Use

Do not modify this field.

Page Erase

Write a 1 to this field to initiate a page erase at the address in FLC_ADDR.addr. The

flash must be unlocked prior to attempting a page erase, see FLC_CTRL.unlock for

details.

The Flash Controller hardware clears this bit when a page erase operation is complete.

0: No page erase operation in process or page erase is complete.

1: Write a 1 to initiate a page erase. If this field reads 1, a page erase operation is in

progress.

Note: This field is protected and cannot be set to 0 by application code.

Mass Erase

Write a 1 to this field to initiate a mass erase of the internal flash memory. The flash

must be unlocked prior to attempting a mass erase, see FLC_CTRL.unlock for details.

The Flash Controller hardware clears this bit when the mass erase operation

completes.

0: No operation

1: Initiate mass erase

Note: This field is protected and cannot be set to 0 by application code.

Write

If this field reads 0, no write operation is pending for the flash. To initiate a write

operation, set this bit to 1 and the Flash Controller will write to the address set in the

FLC_ADDR register.

0: No write operation in process or write operation complete.

1: Write 1 to initiate a write operation. If this field reads 1, a write operation is in

progress.

Note: This field is protected and cannot be set to 0 by application code.

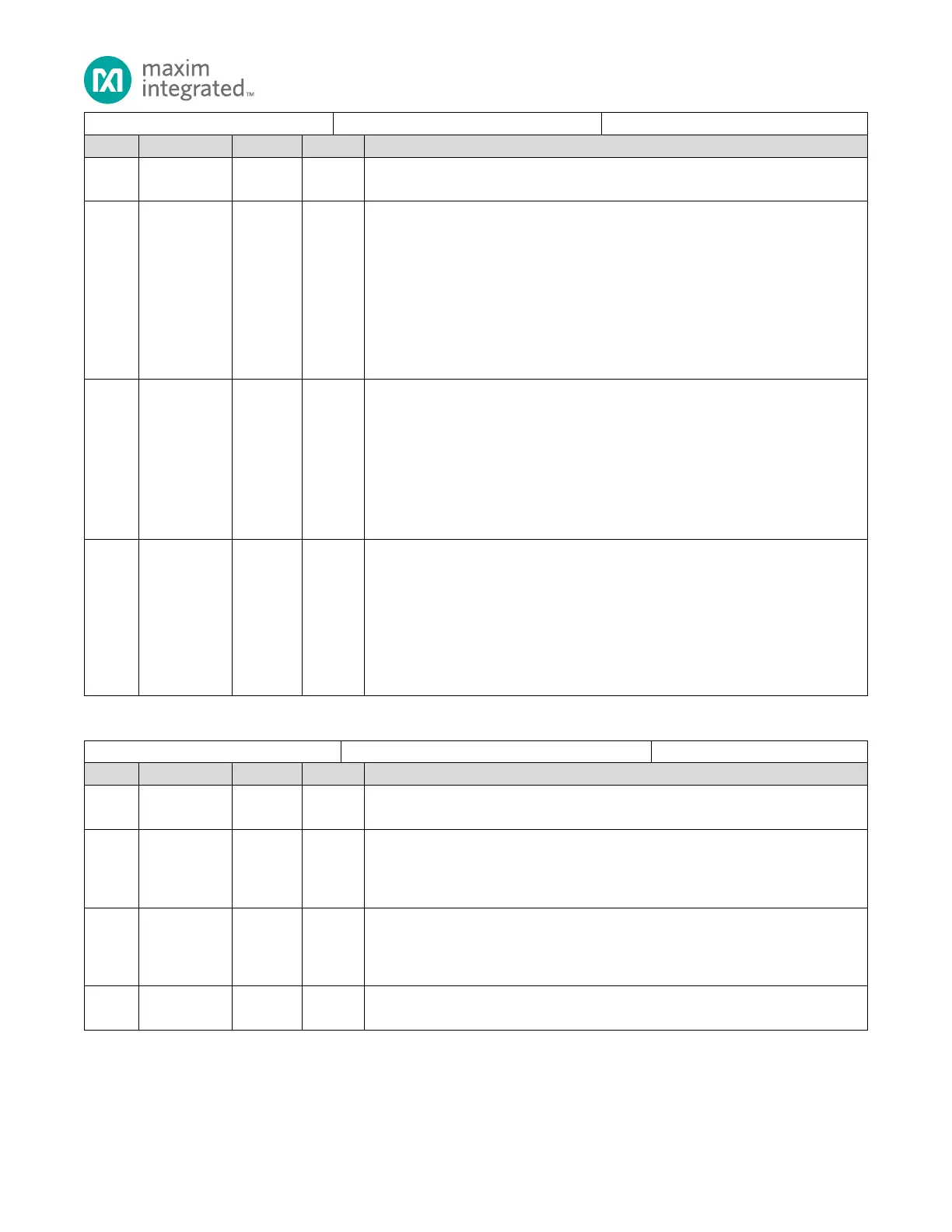

Table 5-5: Flash Controller Interrupt Register

Flash Controller Interrupt Register

Reserved for Future Use

Do not modify this field.

Flash Access Fail Interrupt Enable

Set this bit to 1 to enable interrupts on flash access failures.

0: Disabled

1: Enabled

Flash Operation Complete Interrupt Enable

Set this bit to 1 to enable interrupts on flash operations complete.

0: Disabled

1: Enabled

Reserved for Future Use

Do not modify this field.

Loading...

Loading...