MAX32660 User Guide

Maxim Integrated Page 34 of 195

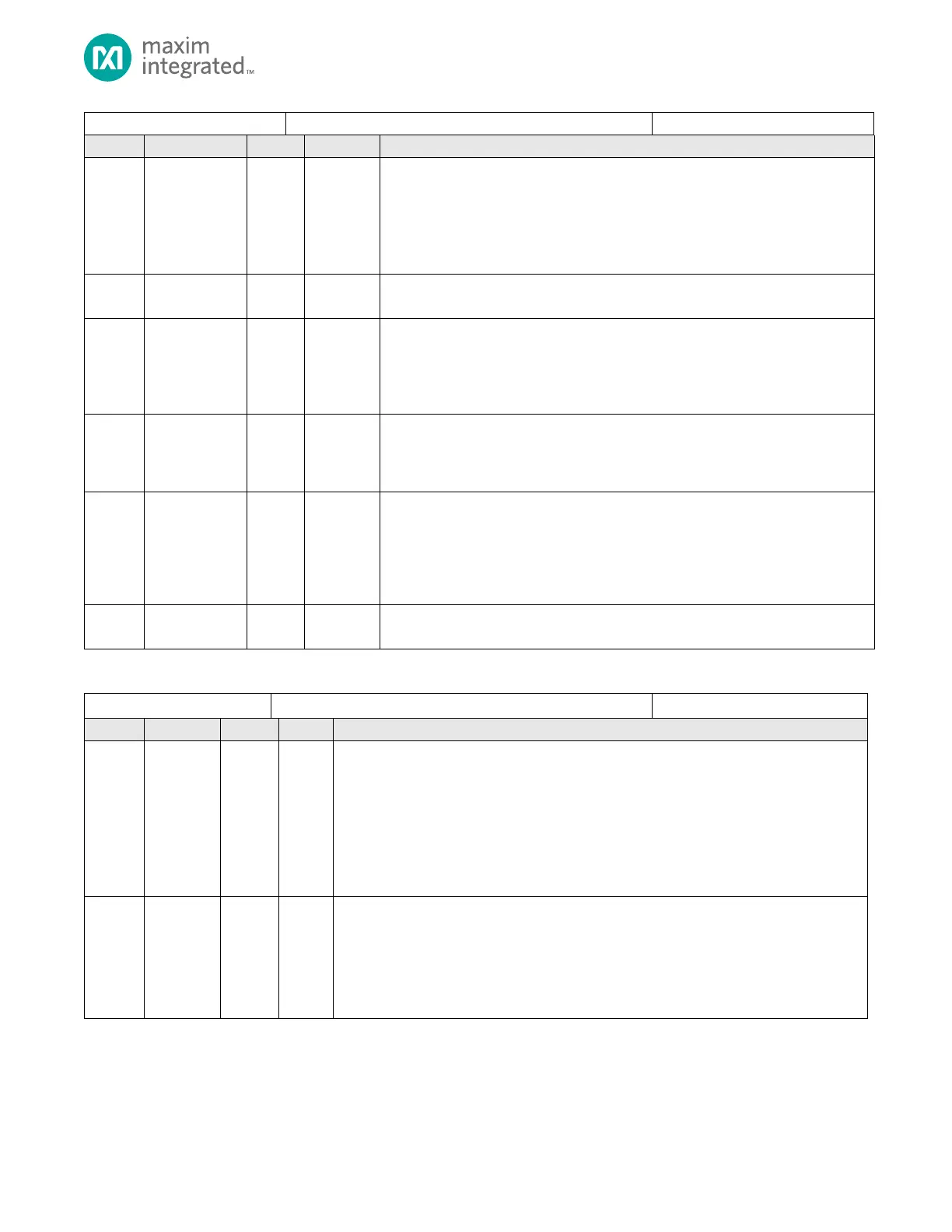

Serial Wire Debug Disable

0: JTAG SWD enabled.

1: JTAG SWD disabled.

Note: If the Arm ICE is unlocked (GCR_SYS_ST.icelock=0), the POR reset value for this

bit is 0. If the Arm ICE is locked (GCR_SYS_ST.icelock=1), the POR reset value for this

bit is 1 and is not writable.

Reserved for Future Use

Do not modify this field.

Instruction Cache Controller Flush

Write 1 to flush the internal flash cache. This bit is cleared by hardware when the

flush is complete.

0: Flush not in process.

1: Write 1 to flush the code cache.

Floating Point Unit (FPU) Disable

Set this field to 1 to disable the Cortex-M4 Floating Point Unit.

0: FPU enabled.

1: FPU disabled.

Flash Page Flip Flag

Flips the bottom and top halves of the internal flash memory. This bit is controlled by

hardware. Firmware should not change the state of this bit during normal operation.

Any change to this bit flushes the instruction cache and the data cache

0: Physical layout matches logical layout

1: Top and Bottom halves flipped.

Reserved for Future Use

Do not modify this field.

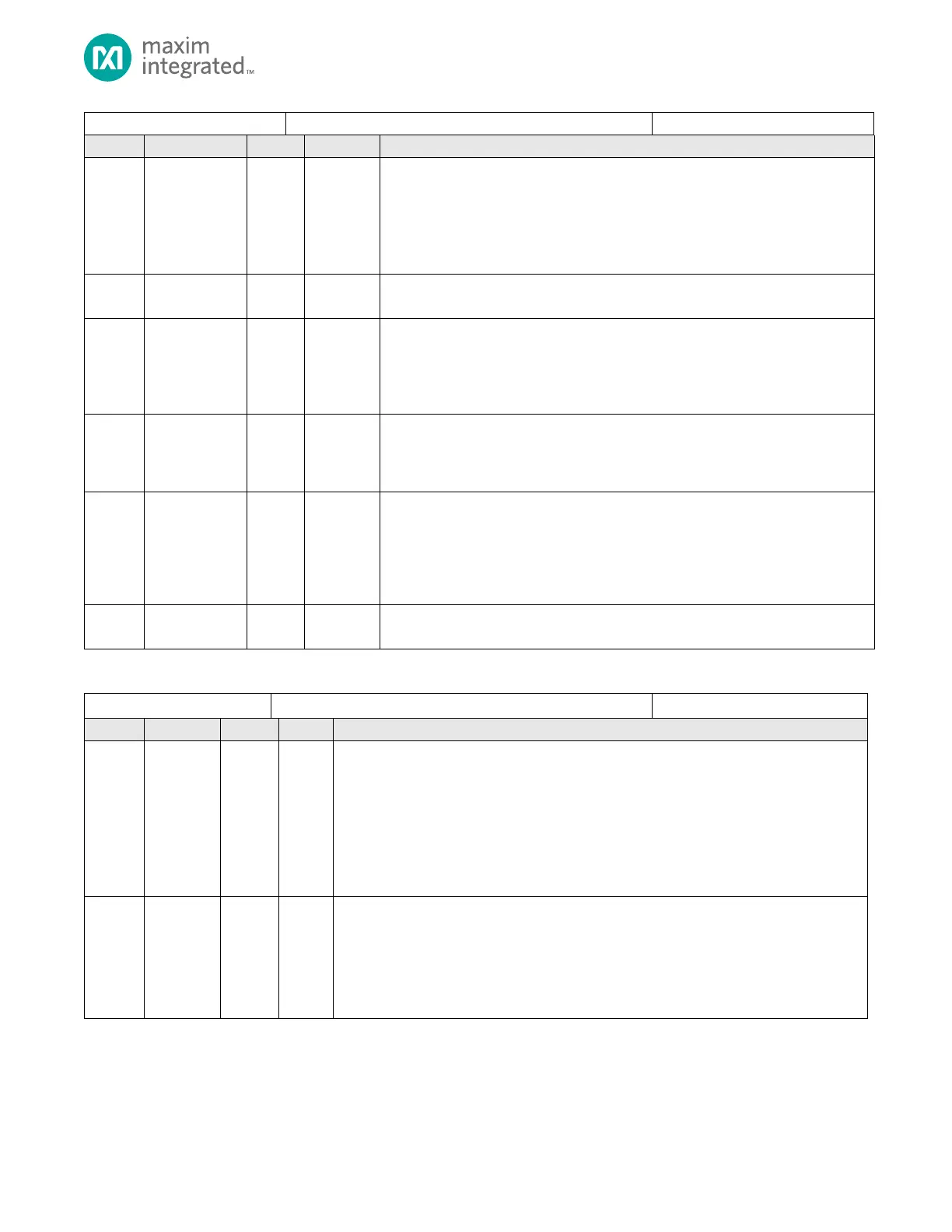

Table 4-14: Reset 0 Register

System Reset

Write 1 to perform a System Reset of the MAX32660. When set to 1, the system reset resets

everything on the device except the AoD registers and the RAM retention. All other

registers, peripherals, the CPU core and the watchdog timer are reset. This field is cleared

by hardware when the reset is complete.

0: Reset complete.

1: Write 1 to perform a System Reset.

Refer to the Device Resets section for additional information.

System Peripheral Reset

Write 1 to perform a Peripheral Reset. All peripherals are reset except for the GPIO port pin

configuration and Watchdog Timer.

0: Reset complete.

1: Write 1 to perform the Peripheral reset.

Refer to the Device Resets section for additional information.

Loading...

Loading...