MAX32660 User Guide

Maxim Integrated Page 64 of 195

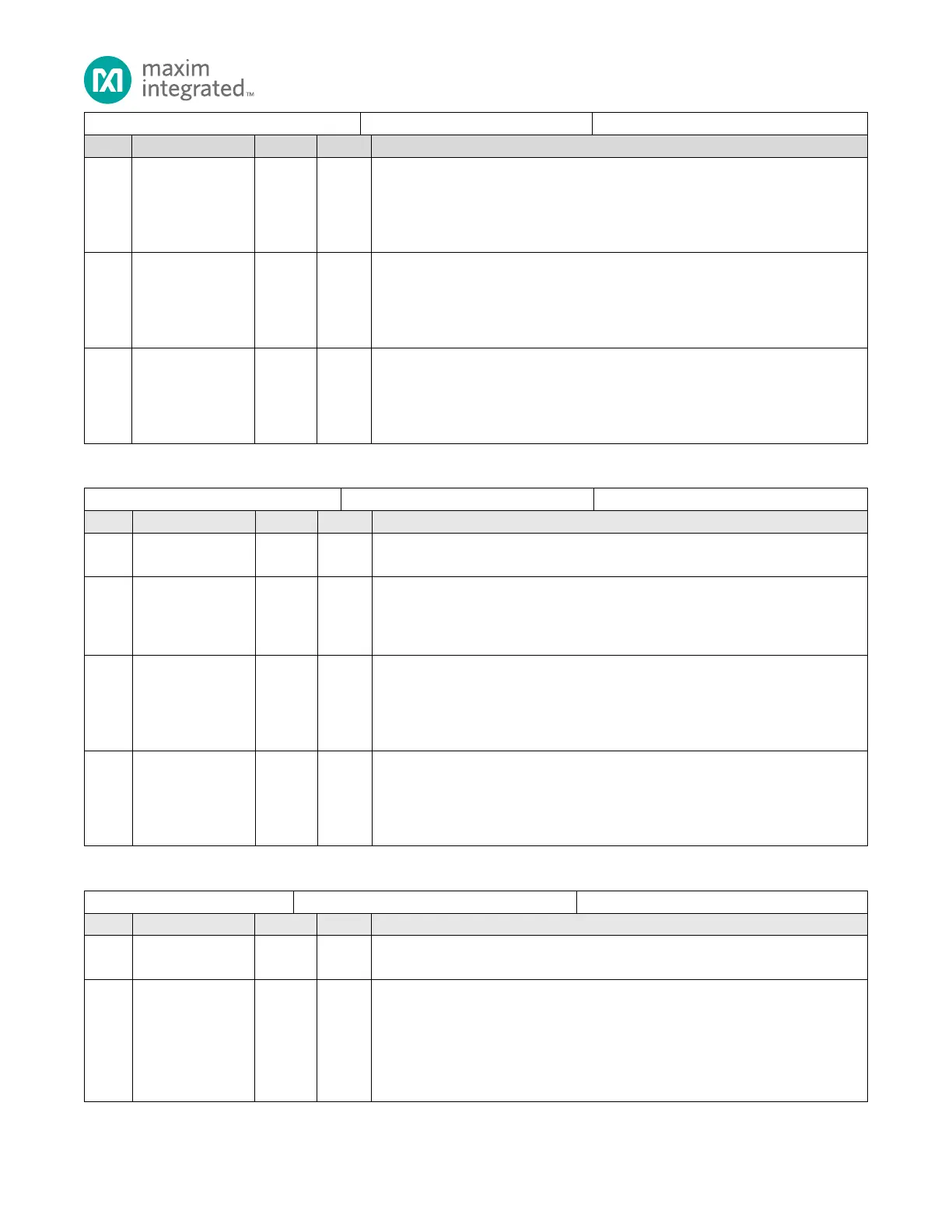

GPIO Alternate Function 0 Select Register

GPIO Alternate Function 0 Mode Select

If JTAG debug is available on the part, this pin defaults to the JTAG alternate function

(TCK/SWCLK) on all forms of reset.

0: Alternate function JTAG TCK/SWCLK enabled (default).

1: GPIO enabled

GPIO Alternate Function 0 Mode Select

If JTAG debug is available on the part, this pin defaults to the JTAG alternate function

(TMS/SWDIO) on all forms of reset.

0: Alternate function JTAG TMS/SWDIO enabled (default).

1: GPIO enabled

GPIO Enable

If JTAG debug is available on the part, this pin defaults to the JTAG alternate function

(TDO) on all forms of reset.

0: Alternate function JTAG TDO enabled (default).

1: GPIO enabled

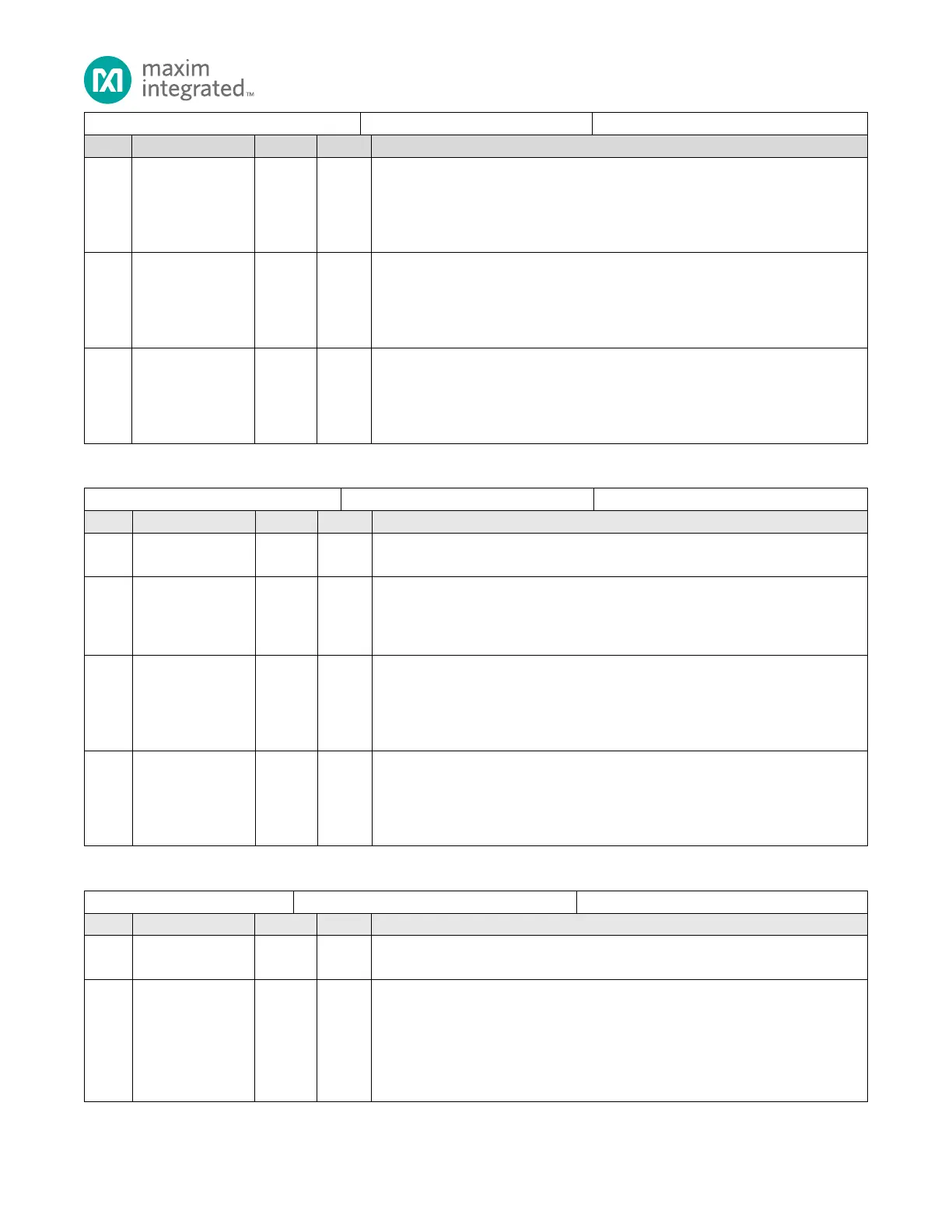

Table 6-10: GPIO Output Enable Register

Reserved for Future Use

Do not modify this field.

GPIO Output Enable

Setting a bit to 1 enables the output driver for the respective pin.

0: Output mode disabled, output driver disabled.

1: Output mode enabled, output driver enabled.

GPIO Output Enable

This bit is set to 1 on POR and is used for the SWDIO alternate function with the

output driver enabled.

0: Output mode disabled, output driver disabled.

1: Output mode enabled, output driver enabled.

GPIO Output Enable

This bit is set to 0 on POR and is used for the SWDCLK alternate function with the

output driver disabled. Setting this bit to 1 enables the output driver for the pin.

0: Output mode disabled, output driver disabled.

1: Output mode enabled, output driver enabled.

Table 6-11: GPIO Output Register

Reserved for Future Use

Do not modify this field.

GPIO Output Level

Set the corresponding output pin high or low.

0: Drive the corresponding output pin low (logic 0).

1: Drive the corresponding output pin high (logic 1).

Note: This bit is ignored if the corresponding bit position in the GPIO0_OUT_EN

register is not set or if the pin is configured for an alternate function.

Loading...

Loading...