MAX32660 User Guide

Maxim Integrated Page 151 of 195

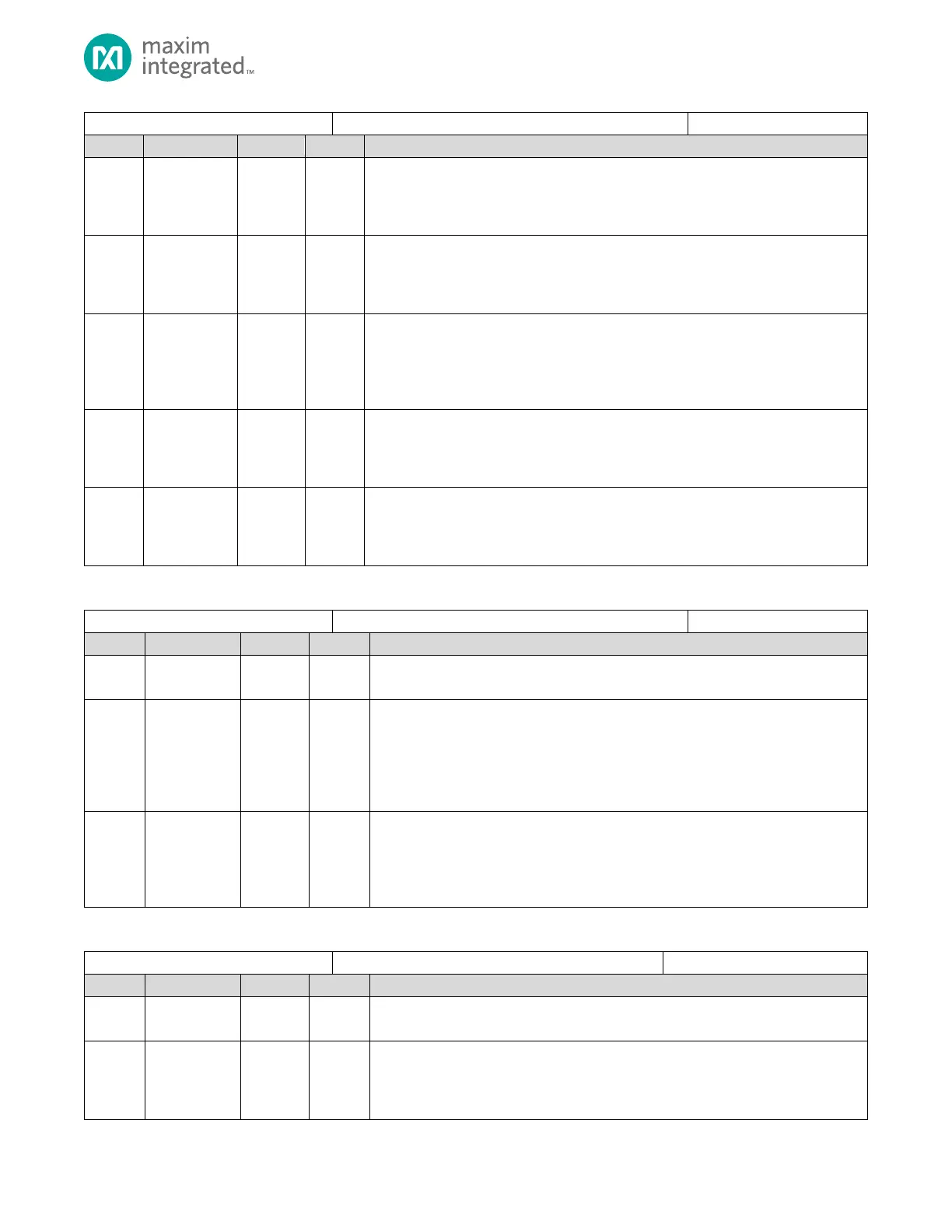

I

2

C Interrupt Enable 0 Register

RX FIFO Threshold Level Interrupt Enable

Set this field to enable interrupt events when an RX FIFO threshold event occurs.

0: Interrupt disabled.

1: Interrupt enabled.

Slave Mode Incoming Address Match Interrupt Enable

Set this field to enable the slave mode address match interrupt event.

0: Interrupt disabled.

1: Interrupt enabled.

Slave Mode General Call Address Match Received Interrupt Enable

Set this field to enable the slave mode general call address match received interrupt

event.

0: Interrupt disabled.

1: Interrupt enabled.

Interactive Receive Interrupt Enable

Set this field to enable the interactive receive interrupt event.

0: Interrupt disabled.

1: Interrupt enabled.

Transfer Complete Interrupt Enable

Set this field to enable the transfer complete interrupt event.

0: Interrupt disabled.

1: Interrupt enabled.

Table 12-8: I

2

C Interrupt Status Flags 1 Registers

I

2

C Interrupt Status Flags 1 Register

Reserved for Future Use

Do not modify this field.

Slave Mode: TX FIFO Underflow Status Flag

In Slave Mode operation, the hardware sets this flag automatically if the TX FIFO is

empty and the master requests more data by sending an ACK after the previous byte

transferred.

0: Slave mode TX FIFO underflow condition has not occurred.

1: Slave mode TX FIFO underflow condition occurred.

Slave Mode: RX FIFO Overflow Status Flag

In Slave Mode operation, the hardware sets this flag automatically when an RX FIFO

overflow occurs. Write 1 to clear. Writing 0 has no effect.

0: Slave mode RX FIFO overflow event has not occurred.

1: Slave mode RX FIFO overflow condition occurred (data lost).

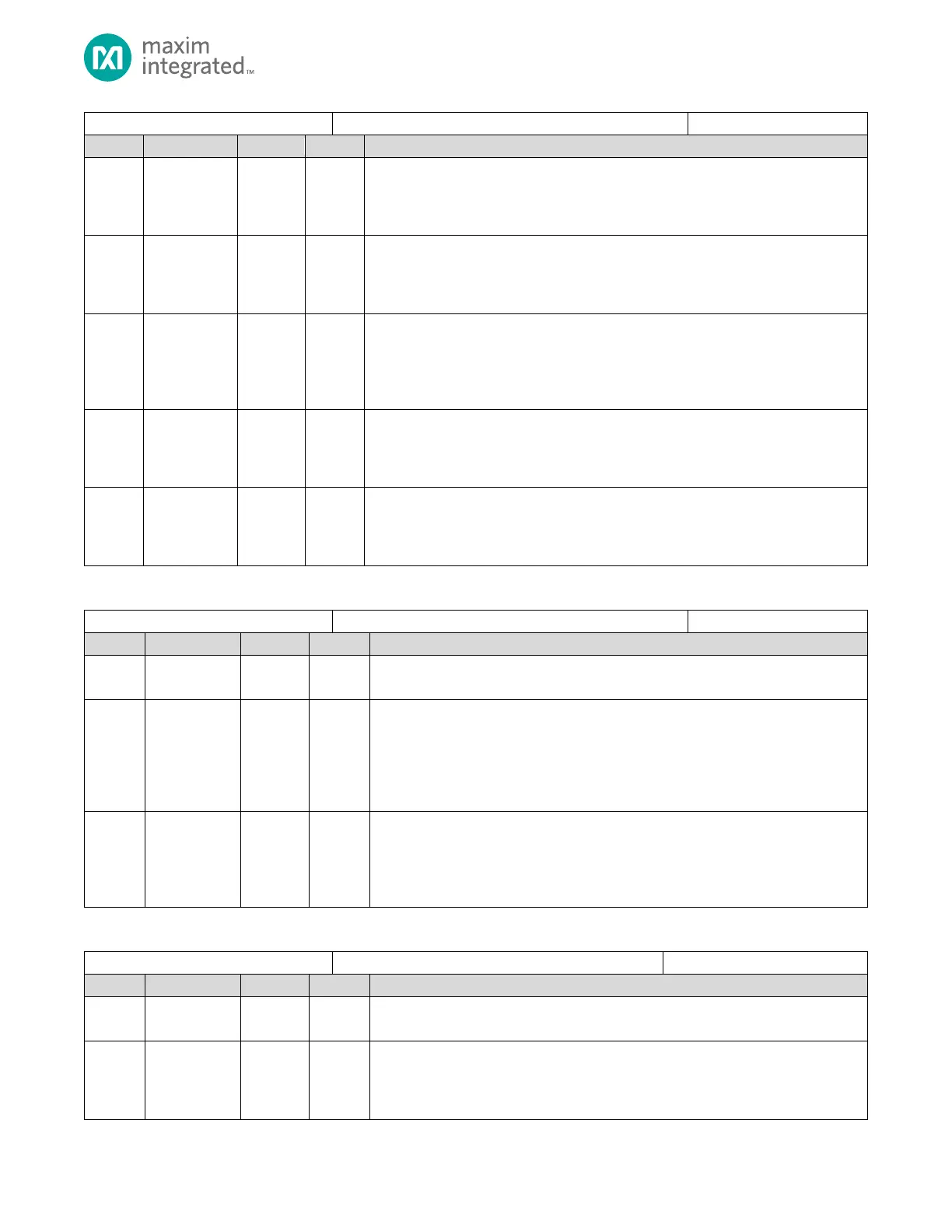

Table 12-9: I

2

C Interrupt Enable Registers 1

I

2

C Interrupt Enable 1 Register

Reserved for Future Use

Do not modify this field.

Slave Mode TX FIFO Underflow Interrupt Enable

In slave mode operation, set this field to enable the TX FIFO underflow interrupt.

0: Interrupt disabled.

1: Interrupt enabled.

Loading...

Loading...