MAX32660 User Guide

Maxim Integrated Page 146 of 195

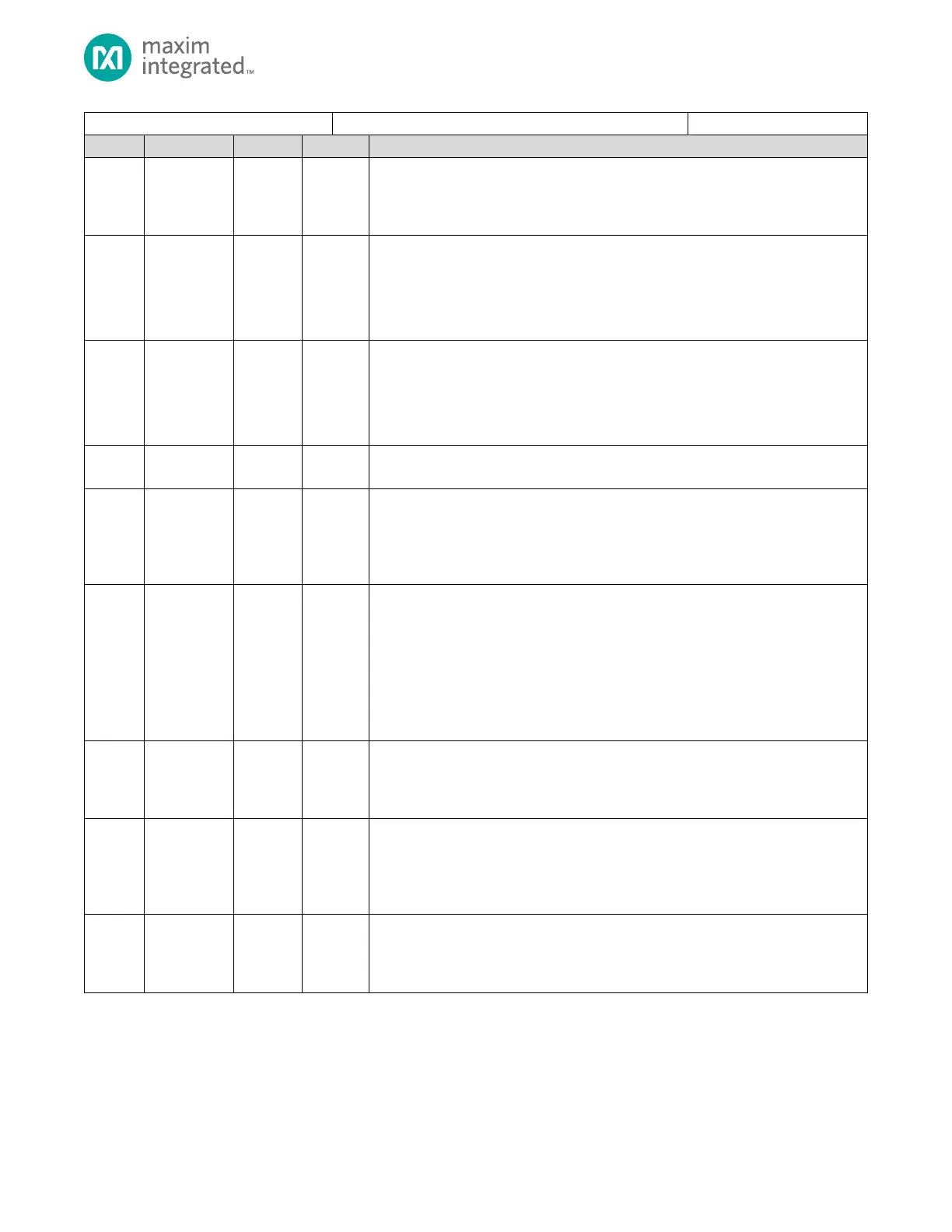

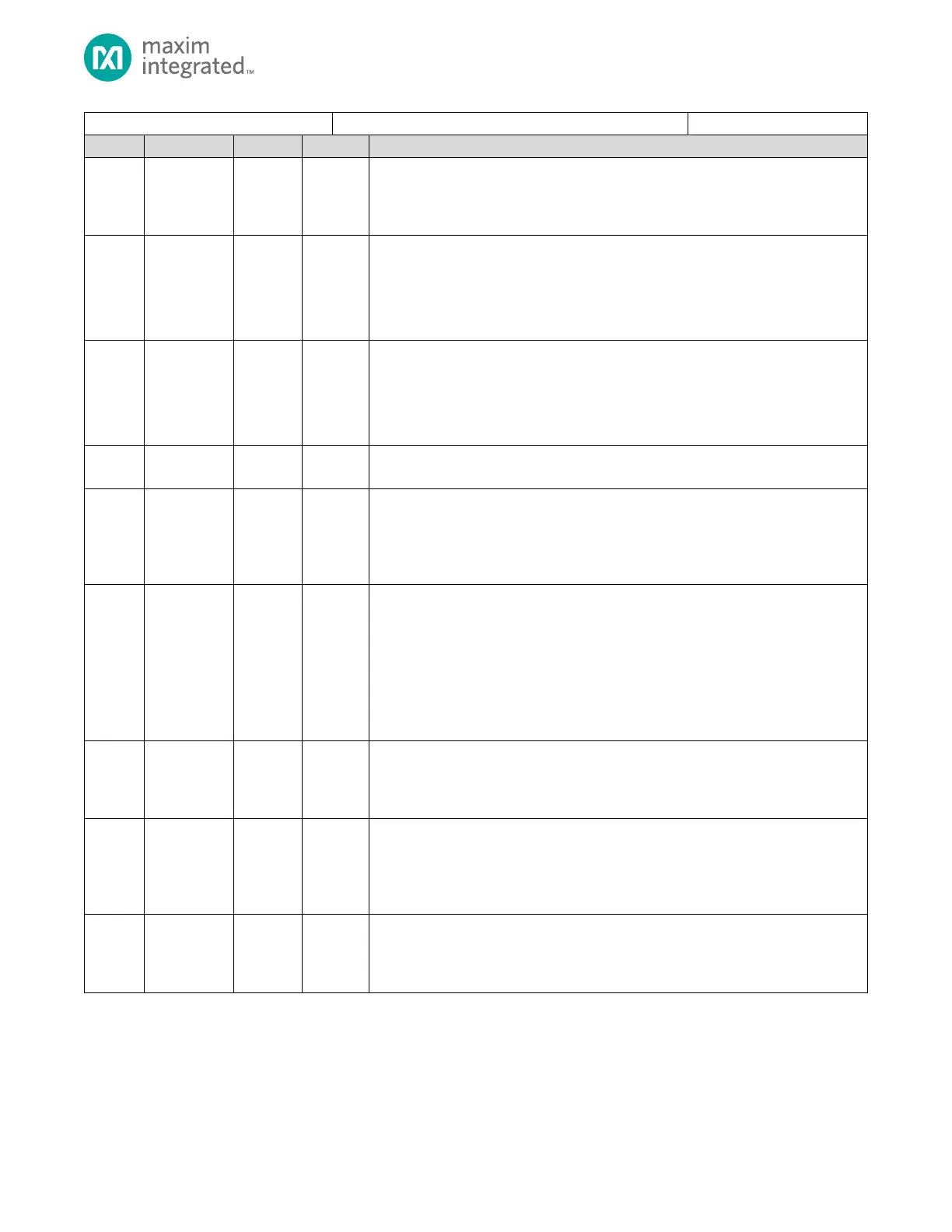

SCL Status

Returns the current logic level of the SCL hardware pin.

0: SCL pin is logic low.

1: SCL pin is logic high.

SDA Pin Control

Set the state of the SDA hardware pin (actively pull low or float).

0: Pull SDA Low

1: Release SDA

Note: Only valid when I2Cn_CTRL0.swoe = 1

SCL Pin Control

Set the state of the SCL hardware pin (actively pull low or float).

0: Pull SCL low

1: Release SCL

Note: Only valid when I2Cn_CTRL0.swoe=1

Reserved for Future Use

Do not modify this field.

Interactive Receive Mode (IRXM) Acknowledge

If IRM is enabled (I2Cn_CTRL0.irxm = 1), this field determines if the hardware sends

an ACK or a NACK to an IRM transaction.

0: Respond to IRM with ACK

1: Respond to IRM with NACK

Interactive Receive Mode (IRXM)

When receiving data, allows for an Interactive Receive Mode (IRM) interrupt event

after each received byte of data. The I

2

C peripheral hardware can be enabled to send

either an ACK or NACK for IRM. See Interactive Receive Mode section for detailed

information.

0: Disable Interactive Receive Mode

1: Enable Interactive Receive Mode

Note: Only set this field when the I

2

C bus is inactive.

General Call Address Enable

Set this field to 1 to enable General Call Address Acknowledgement.

0: Ignore General Call Address

1: Acknowledge General Call Address

Master Mode Enable

Setting this field to 1 enables Master mode operation for the I

2

C peripheral. Setting

this field to 0 enables the I

2

C peripheral for Slave mode operation.

0: Slave mode enabled

1: Master mode enabled

I

2

C Enable

Set this field to 1 to enable the I

2

C peripheral.

0: I

2

C peripheral disabled

1: I

2

C peripheral enabled

Loading...

Loading...