MAX32660 User Guide

Maxim Integrated Page 170 of 195

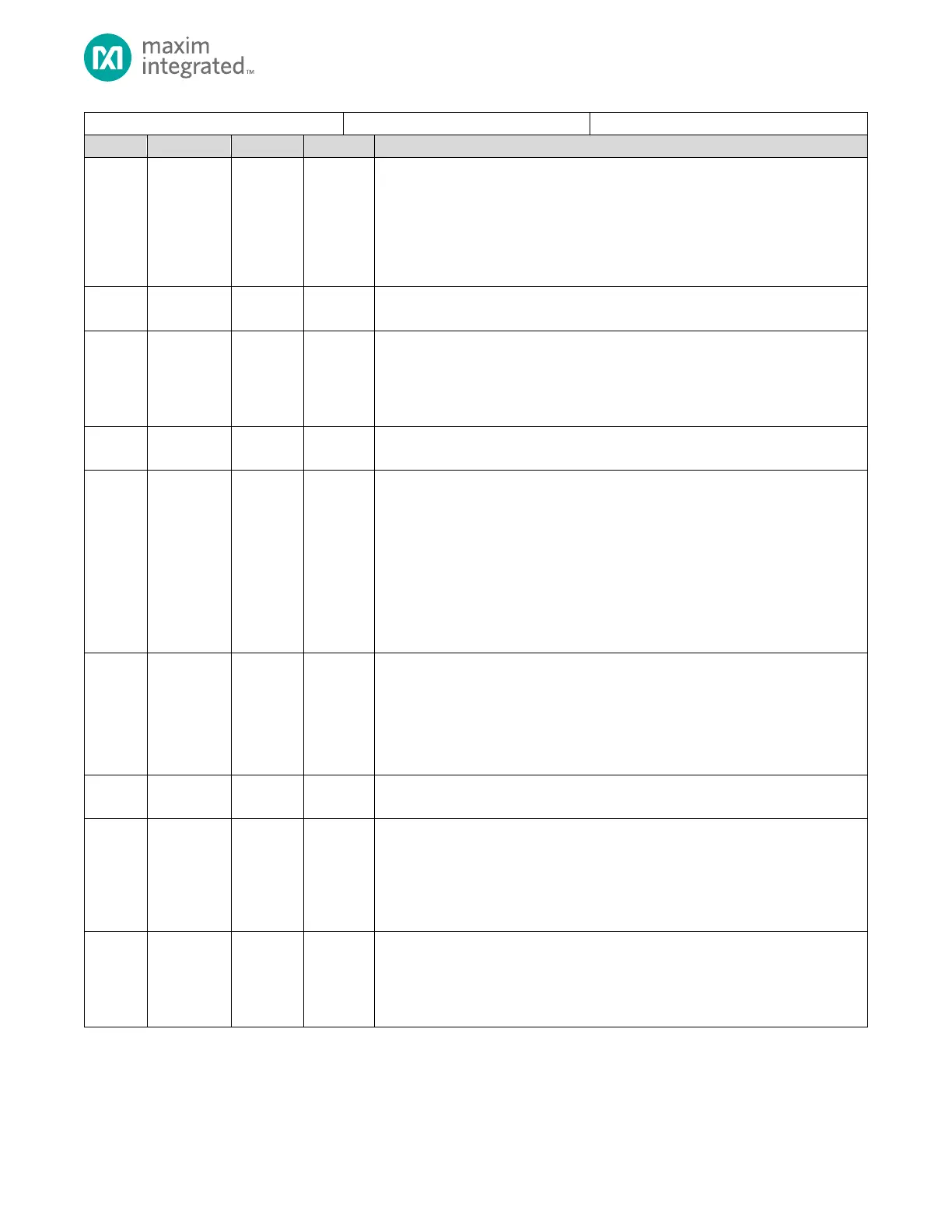

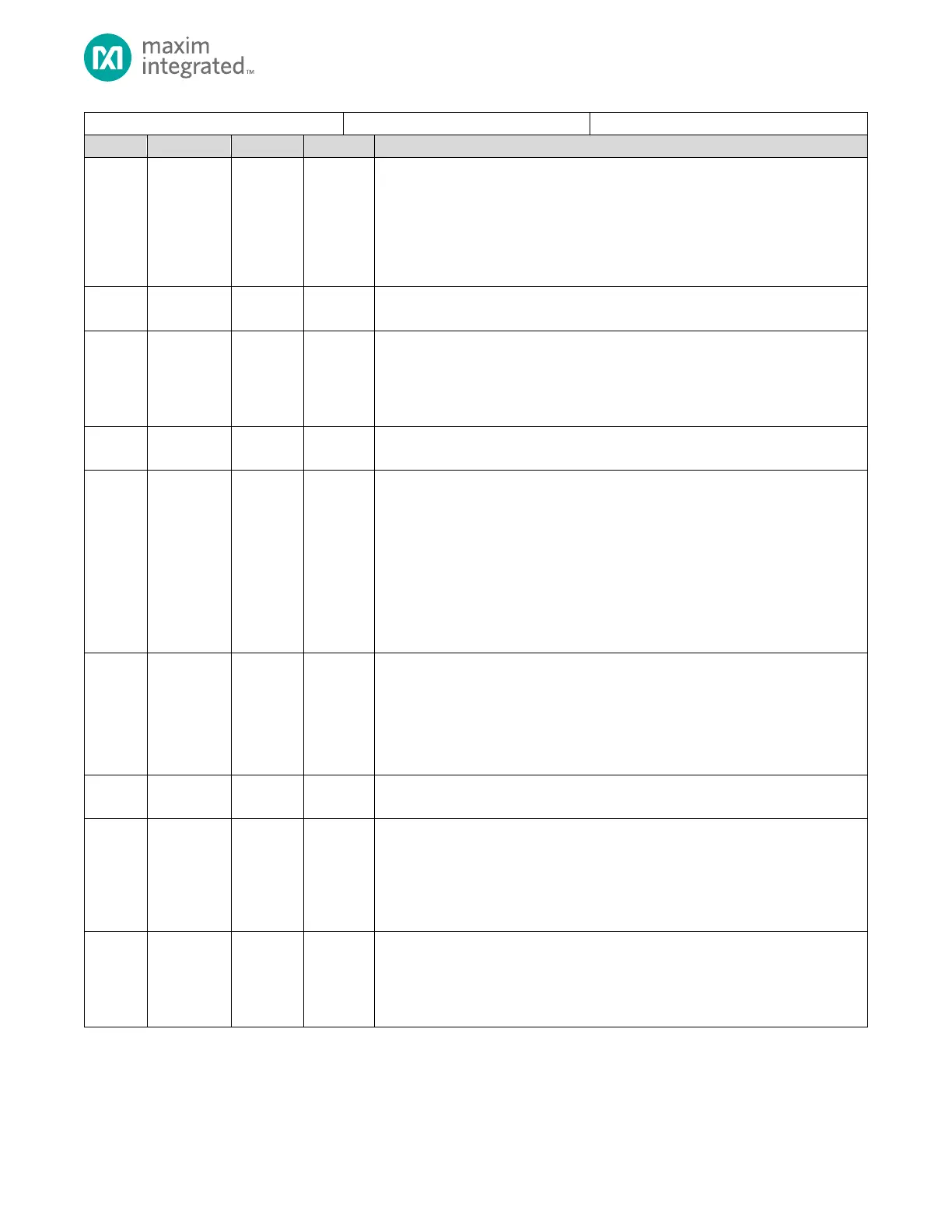

SPI Master Signals Control Register

Slave Select Enable

Set this field to 1 to enable the slave select pin for SPI Master mode. When this field

is set to 1, the SPI0_SS0 pin is used for the slave select output when the next SPI

transaction is started (SPI0_CTRL0.start = 1).

0: SPI0_SS0 is disabled

1: SPI0_SS0 is enabled for output in SPI Master mode operation.

2 15: Reserved for Future Use.

Reserved for Future Use

Do not modify this field.

Master Mode Slave Select Control

In Master Mode operation, this bit controls the state of the slave select line at the

end of a transmission.

0: Slave Select is deasserted at the end of a transmission

1: Slave Select stays asserted at the end of a transmission

Reserved for Future Use

Do not modify this field.

Master Mode Start Data Transmission

This bit is cleared by hardware. Writing a 0 is ignored.

0: Hardware automatically sets this field to 0 when the transaction has been

initiated.

1: Master initiates a data transmission. Ensure that all pending transactions are

complete before writing a 1.

Note: At least 1 byte must be loaded in the TX FIFO prior to setting this bit to 1.

Note: This field is only used when the SPI is configured for Master Mode

(SPI0_CTRL0.mm_en = 1).

Master Mode Slave Select Output

This field must be set to 0 for the MAX32660.

0: Slave Select is an output

1: Reserved for Future Use

Note: This field is only used when the SPI is configured for Master Mode

(SPI0_CTRL0.mm_en = 1).

Reserved for Future Use

Do not modify this field.

SPI Master Mode Enable

This field selects between slave mode and master mode operation for the SPI port.

Write this field to 0 to operate as an SPI slave. Setting this field to 1 sets the port as

an SPI master.

0: SPI port is in Slave Mode.

1: SPI is in Master Mode

SPI Enable/Disable

This field enables the SPI port instance. Setting this field disables the SPI port, but

does not change the contents of the receive or transmit FIFOs or other SPI registers.

0: SPI port is disabled

1: SPI port is enabled

Loading...

Loading...