MAX32660 User Guide

Maxim Integrated Page 193 of 195

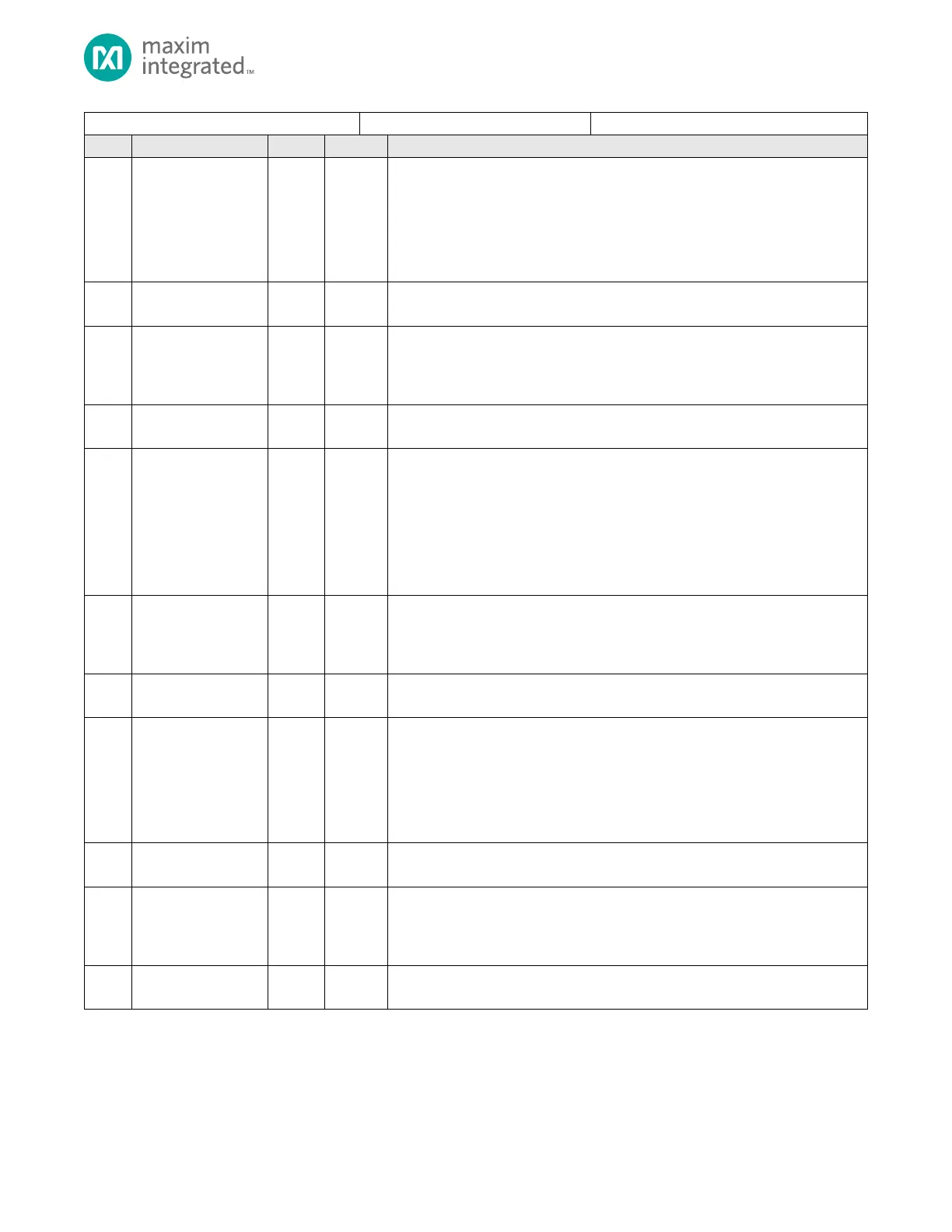

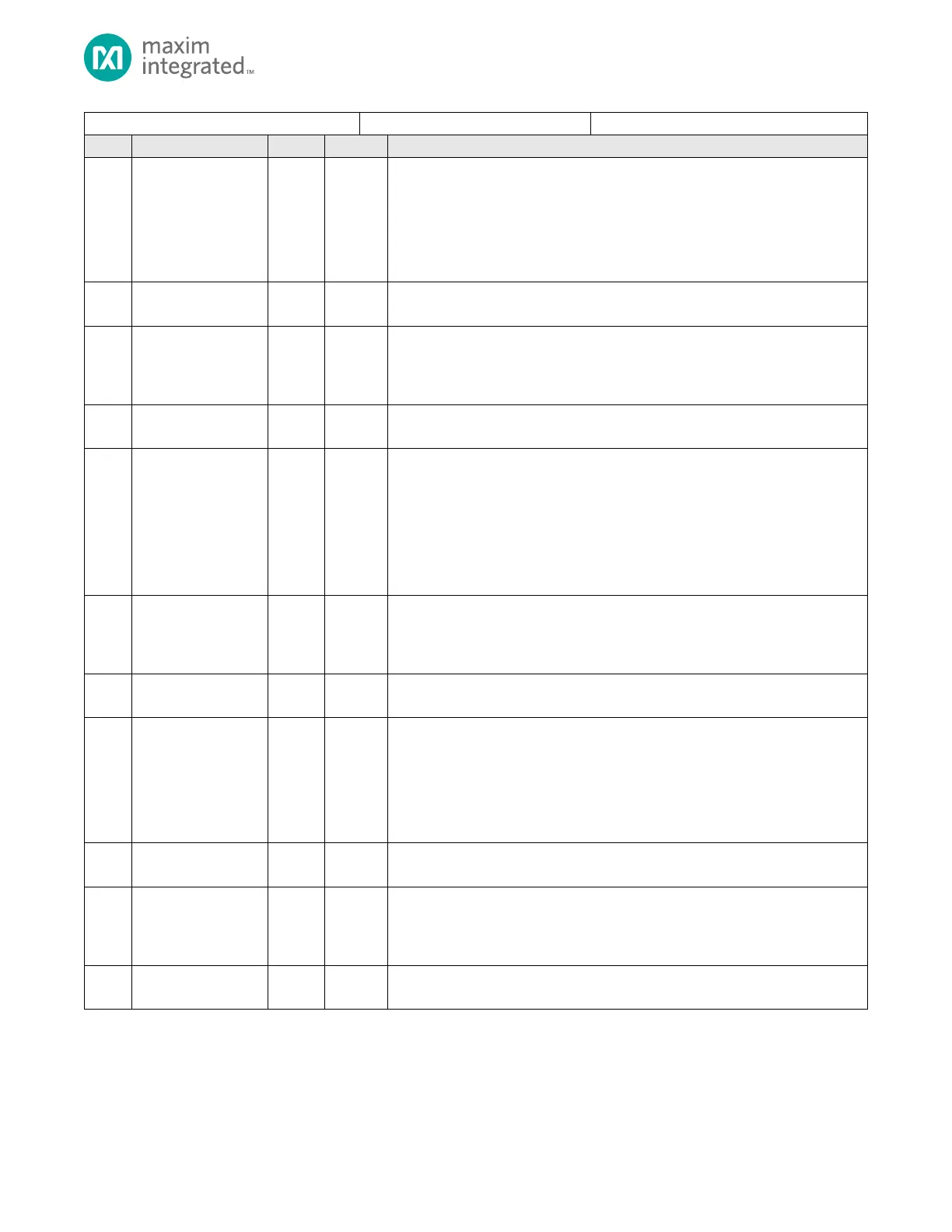

Receive FIFO Count

0b0000: RX FIFO empty (0 entries)

0b0001: RX FIFO contains 1 entry

0b0010: RX FIFO contains 2 entries

0b0011: RX FIFO contains 3 entries

0b1000: RX FIFO contains 15 entries

Reserved for Future Use

Do not modify this field.

Receive FIFO Clear

Write 1 to reset the Receive FIFO. Writing 0 has no effect.

0: Ignored

1: Reset Receive FIFO

Reserved for Future Use

Do not modify this field.

Receive FIFO Level

Sets the RX FIFO DMA request threshold. This configures the number of filled RX

FIFO entries before activating an RX DMA request.

000: Request Receive DMA when RX FIFO contains 1 entry

001: Request Receive DMA when RX FIFO contains 2 entries

010: Request Receive DMA when RX FIFO contains 3 entries

111: Request Receive DMA when RX FIFO contains 8 entries

Transmit DMA Enable

Disabling clears any active request to the DMA controller.

0: Disable TX DMA requests

1: Enable TX DMA requests

Reserved for Future Use

Do not modify this field.

Transmit FIFO Count

0b0000: TX FIFO empty (0 entries)

0b0001: TX FIFO contains 1 entry

0b0010: TX FIFO contains 2 entries

0b0011: TX FIFO contains 3 entries

0b1000: TX FIFO contains 15 entries

Reserved for Future Use

Do not modify this field.

Transmit FIFO Clear

Write 1 to reset the Receive FIFO. Writing 0 has no effect.

0: Ignored

1: Reset Receive FIFO

Reserved for Future Use

Do not modify this field.

Loading...

Loading...