MAX32660 User Guide

Maxim Integrated Page 41 of 195

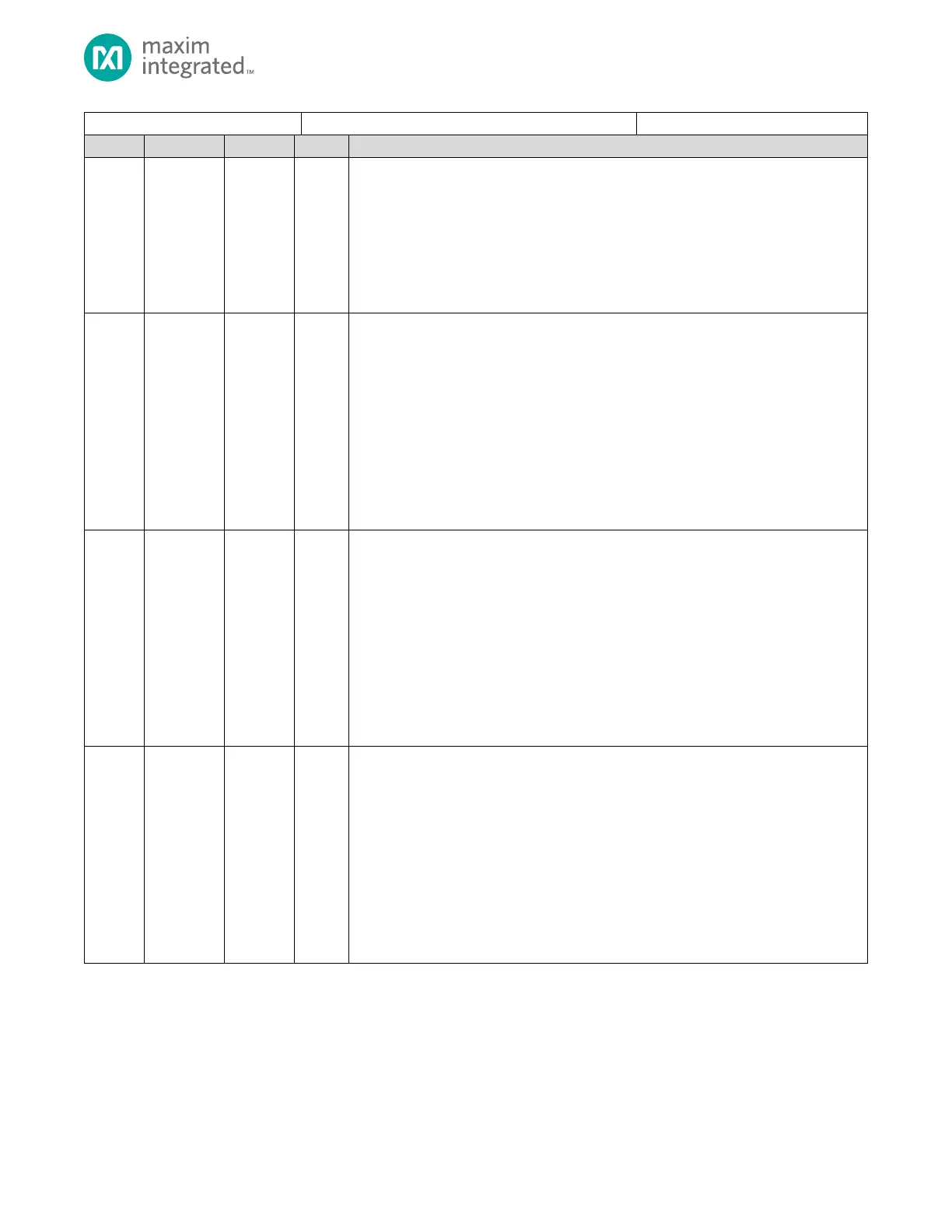

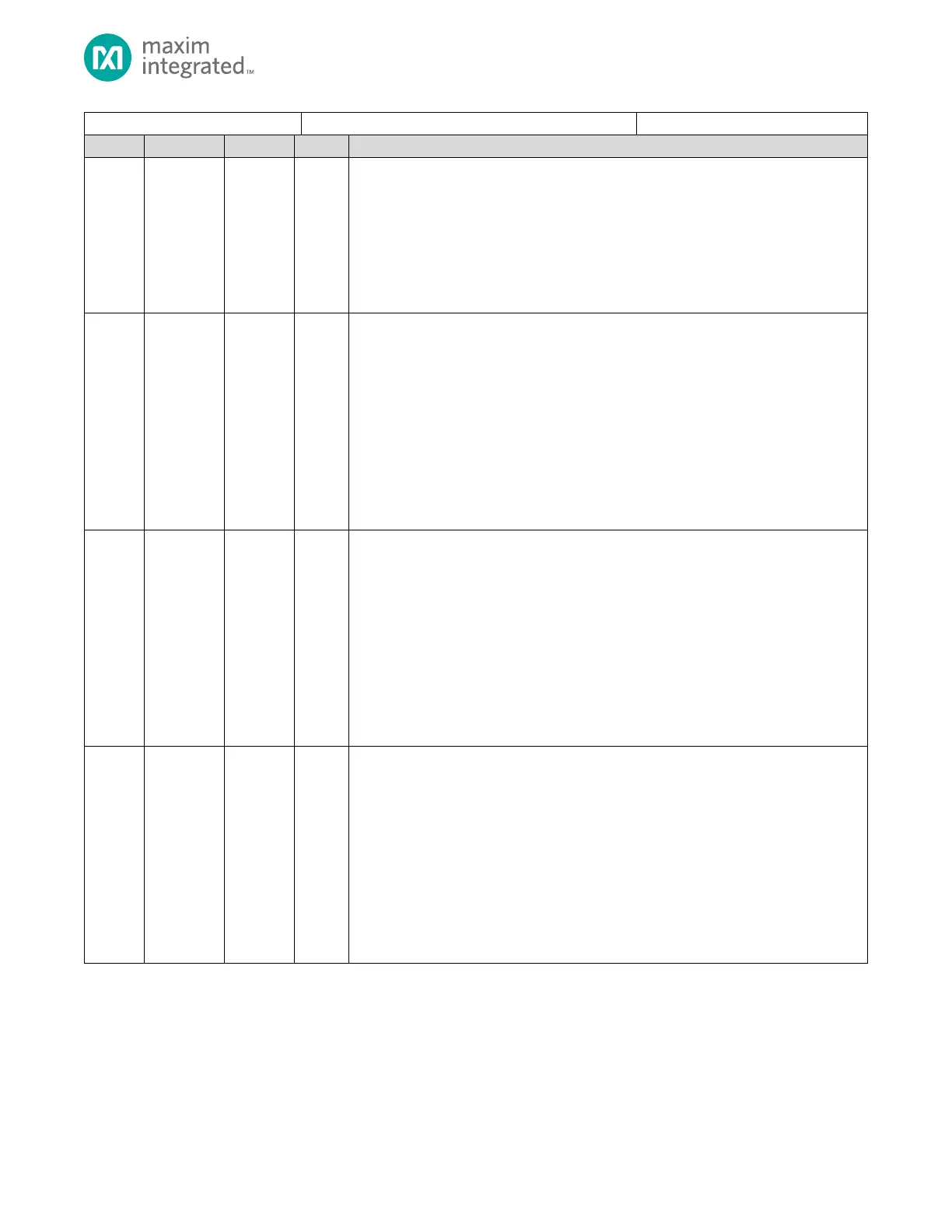

Memory Clock Control Register

ICC0 Cache RAM Light Sleep Enable

RAM. Setting this field to 1 retains the state of the cache but the cache is not accessible.

This is useful if executing code from RAM or while in SLEEP mode operation.

0: ICC0 Cache RAM is active.

1: ICC0 Cache RAM is in Light Sleep mode.

Note: Any reset event that results in a Cache RAM reset will reset the Cache RAM

regardless of the state of this field.

System RAM 3 Light Sleep Enable

Set this field to 1 to enable Light Sleep for System RAM 3 (0x2001 0000 - 0x2001 7FFF). In

Light Sleep mode, the System RAM contents are retained but the Data Memory cannot

be read.

0: System RAM 3 retention is not enabled.

1: System RAM 3 is in Light Sleep mode.

Note: Any reset event that results in RAM reset will reset the RAM regardless of the state

of this field.

Note: To put RAM in a shutdown mode that removes all power from the RAM and reset

the RAM contents, use the register PWRSEQ_LPMEMSD “Low Power Mode RAM Shut

Down Control”.

System RAM 2 Data Retention Enable

Set this field to 1 to enable Light Sleep mode for System RAM 2

(0x2000 8000 - 0x2000 FFFF). In Light Sleep mode, the System RAM contents are retained

but the Data Memory cannot be read.

0: System RAM 2 retention is not enabled

1: System RAM 2 is in Light Sleep mode.

Note: Any reset event that results in RAM reset will reset the RAM regardless of the state

of this field.

Note: To put RAM in a shutdown mode that removes all power from the RAM and reset

the RAM contents, use the register PWRSEQ_LPMEMSD “Low Power Mode RAM Shut

Down Control”.

System RAM 1 Light Sleep Enable

Set this field to 1 to enable Light Sleep for System RAM 1 (0x2000 4000 - 0x2000 7FFF). If

light sleep is enabled, the System RAM contents are retained but the Data Memory

cannot be read.

0: System RAM 1 retention is not enabled

1: System RAM 1 data retention is enabled for BACKUP mode.

Note: Any reset event that results in RAM reset will reset the RAM regardless of the state

of this field.

Note: To put RAM in a shutdown mode that removes all power from the RAM and reset

the RAM contents, use the register PWRSEQ_LPMEMSD “Low Power Mode RAM Shut

Down Control”.

Loading...

Loading...