4

4-11

EIT

32180 Group User’s Manual (Rev.1.0)

4.8 Exception Processing

4.8 Exception Processing

4.8.1 Reserved Instruction Exception (RIE)

[Occurrence Conditions]

Reserved Instruction Exception (RIE) occurs when a reserved instruction (unimplemented instruction) is

detected. Instruction check is performed on the op-code part of the instruction.

When a reserved instruction exception occurs, the instruction that generated it is not executed. If an exter-

nal interrupt is requested at the same time a reserved instruction exception is detected, it is the reserved

instruction exception that is accepted.

[EIT Processing]

(1) Saving SM, IE and C bits

The PSW register’s SM, IE and C bits are saved to the respective backup bits: BSM, BIE and BC.

BSM ← SM

BIE ← IE

BC ← C

(2) Updating SM, IE and C bits

The PSW register’s SM, IE and C bits are updated as shown below.

SM ← Unchanged

IE ← 0

C ← 0

(3) Saving the PC

The PC value of the instruction that generated the reserved instruction exception is set in the BPC register.

For example, if the instruction that generated the reserved instruction exception is at address 4, the value 4

is set in the BPC register. Similarly, if the instruction that generated the reserved instruction exception is at

address 6, the value 6 is set in the BPC register. In this case, the value of the BPC register bit 30 indicates

whether the instruction that generated the reserved instruction exception resides on a word boundary (BPC

register bit 30 = "0") or not on a word boundary (BPC register bit 30 = "1").

However, in either case of the above, the address to which the RTE instruction returns after the EIT handler

has terminated is address 4. (This is because the 2 low-order address bits are cleared to ‘00’ when returned

to the PC.)

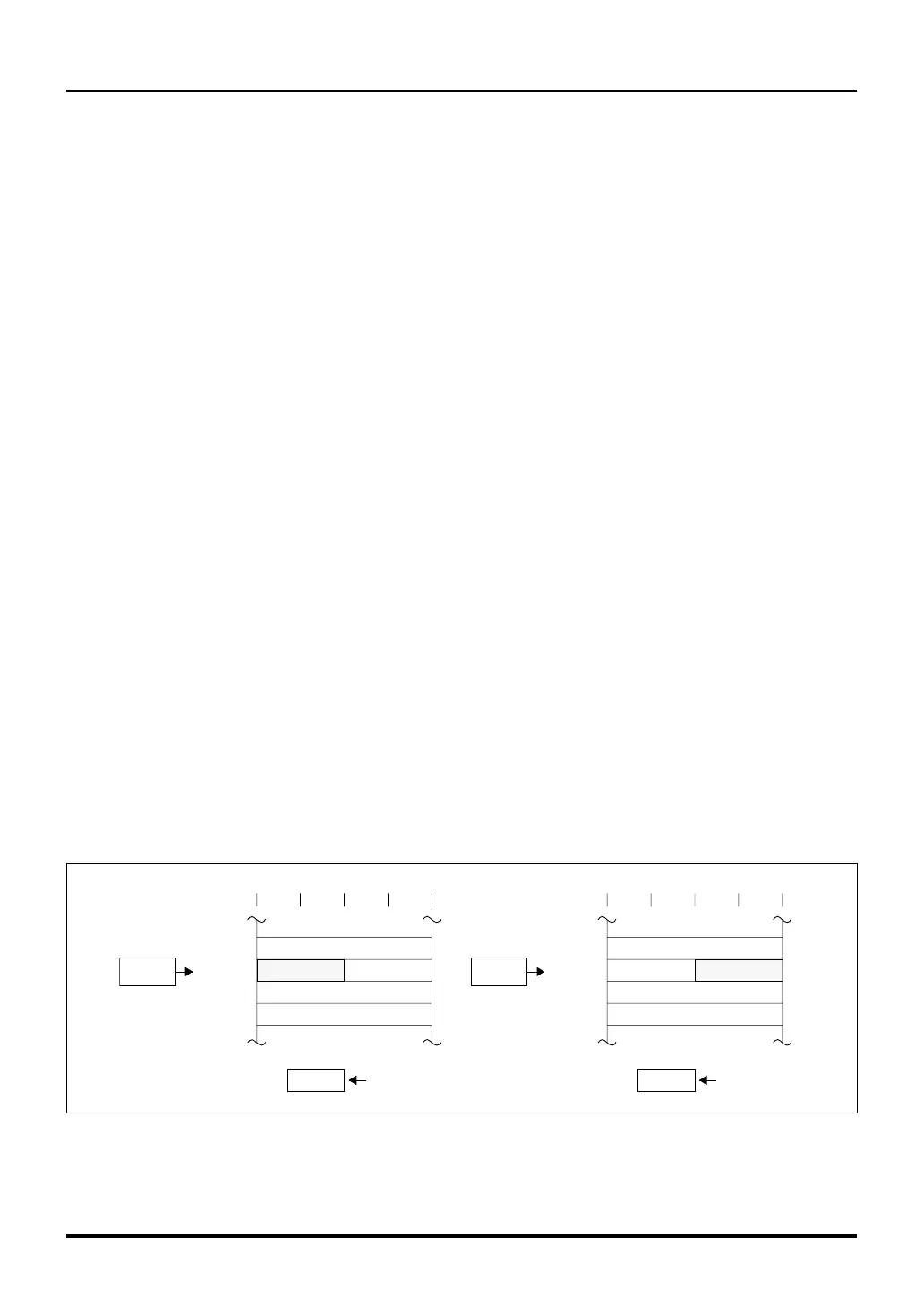

Figure 4.8.1 Example of a Return Address for Reserved Instruction Exception (RIE)

H'00

Address

RIE occurred

H'04

H'08

H'0C

+0 +1 +2 +3

H'00

Address

RIE occurred

H'04

H'08

H'0C

+0 +1 +2 +3

Return

address

BPC

H'06

BPC

H'04

Return

address

Loading...

Loading...