5

5-6

INTERRUPT CONTROLLER (ICU)

32180 Group User’s Manual (Rev.1.0)

5.2 ICU Related Registers

5.2.2 Interrupt Request Mask Register

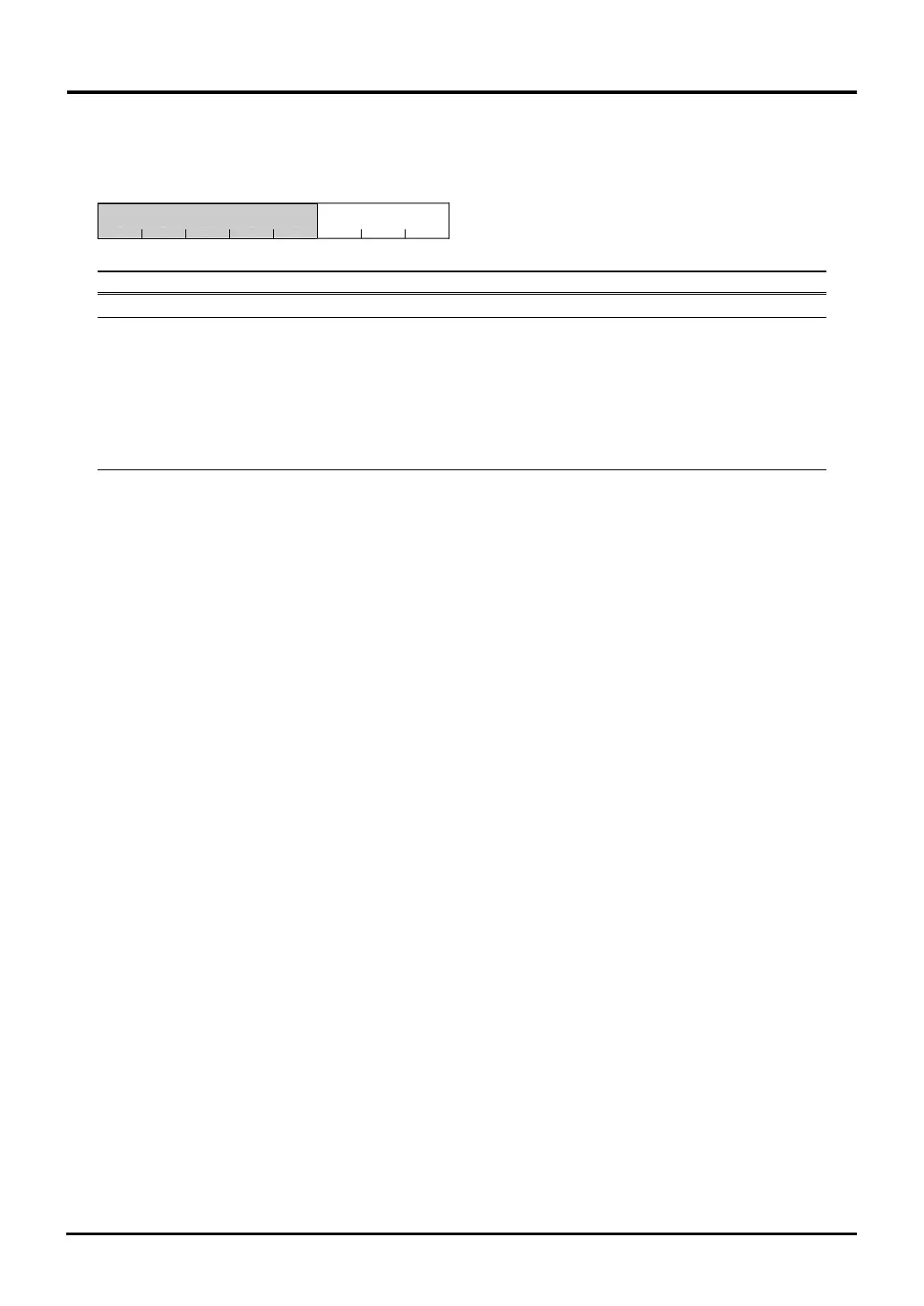

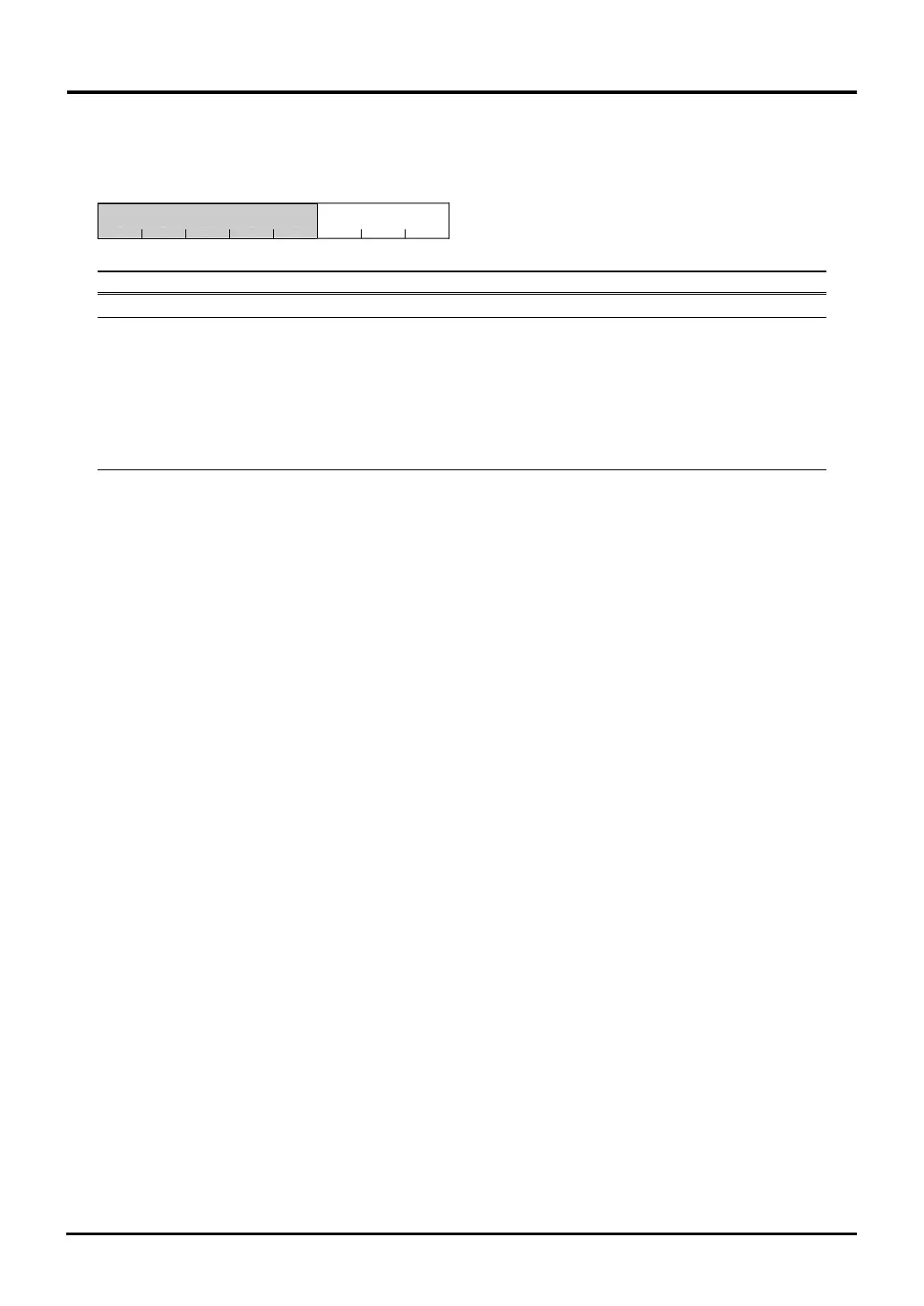

Interrupt Request Mask Register (IMASK) <Address: H’0080 0004>

123456b7b0

IMASK

111

<After reset: H’07>

b Bit Name Function R W

0–4 No function assigned. Fix to "0" 00

5–7 IMASK 000: Disable maskable interrupts R W

Interrupt mask bit 001: Accept interrupts with priority level 0

010: Accept interrupts with priority levels 0–1

011: Accept interrupts with priority levels 0–2

100: Accept interrupts with priority levels 0–3

101: Accept interrupts with priority levels 0–4

110: Accept interrupts with priority levels 0–5

111: Accept interrupts with priority levels 0–6

The Interrupt Request Mask Register (IMASK) is used to finally determine whether or not to accept an interrupt

request after comparing its priority with the priority levels (Interrupt Control Register ILEVEL bits) that have been

set for each interrupt request source.

When the Interrupt Vector Register (IVECT) described above is read, the interrupt priority level of the accepted

interrupt request source is set in this IMASK register as a new mask value.

When any value is written to the IMASK register, operations (1) to (2) below are automatically performed in

hardware.

(1) The interrupt request (EI) to the CPU core is deasserted.

(2) The ICU’s internal sequencer is activated to start internal processing (interrupt priority resolution).

Notes: • Do not write to the Interrupt Request Mask Register (IMASK) in the EIT handler unless interrupts

are disabled (PSW register IE bit = "0").

• To reenable interrupts (by setting the IE bit to "1") after writing to the Interrupt Request Mask

Register (IMASK), perform a dummy access to the internal memory, etc. before reenabling inter-

rupts.

Loading...

Loading...