11

11-16

A-D Converters

32180 Group User's Manual (Rev.1.0)

11.2 A-D Converter Related Registers

11.2.1 A-D Single Mode Registers 0

A-D0 Single Mode Register 0 (AD0SIM0) <Address: H’0080 0080>

A-D1 Single Mode Register 0 (AD1SIM0) <Address: H'0080 0A80>

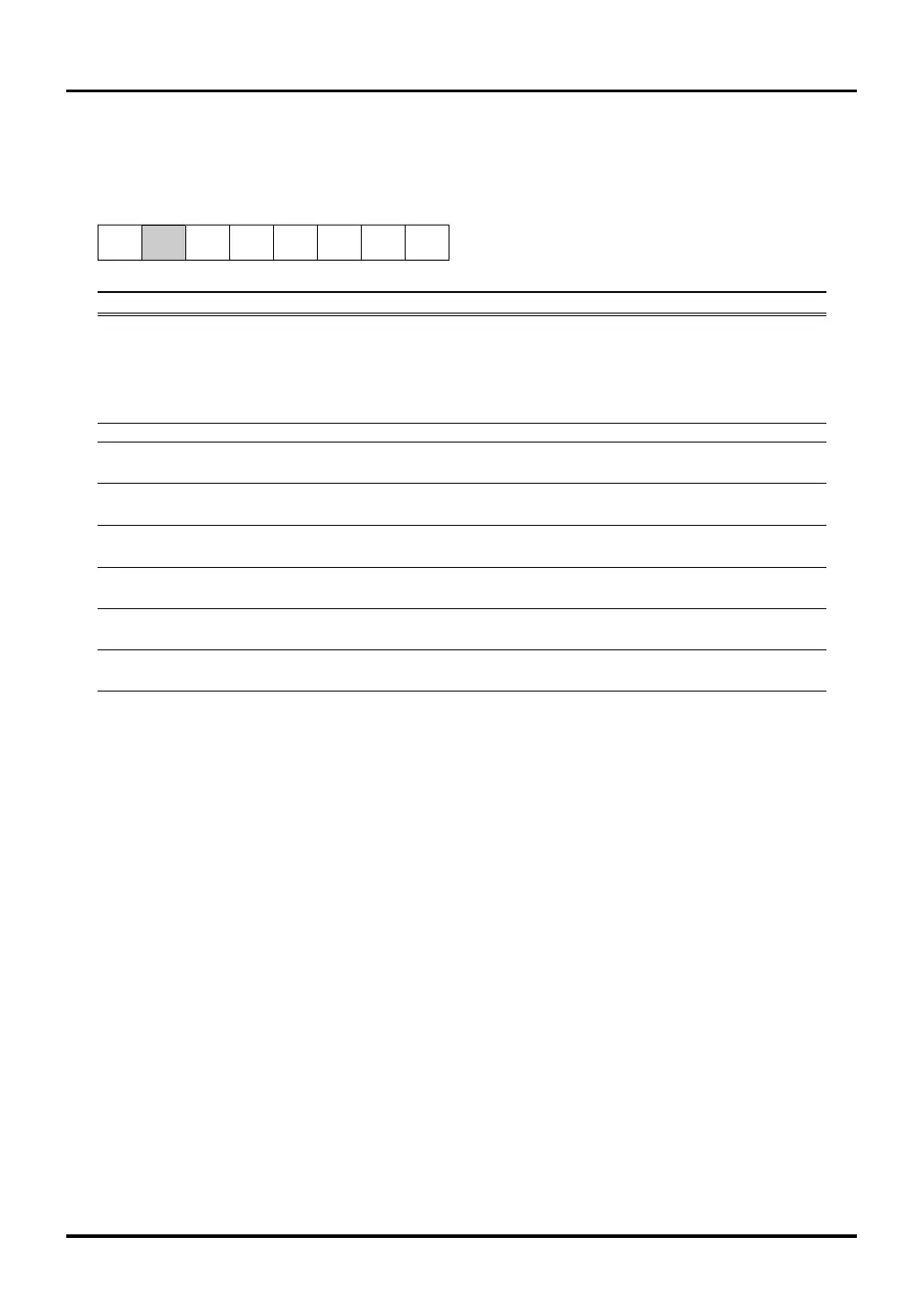

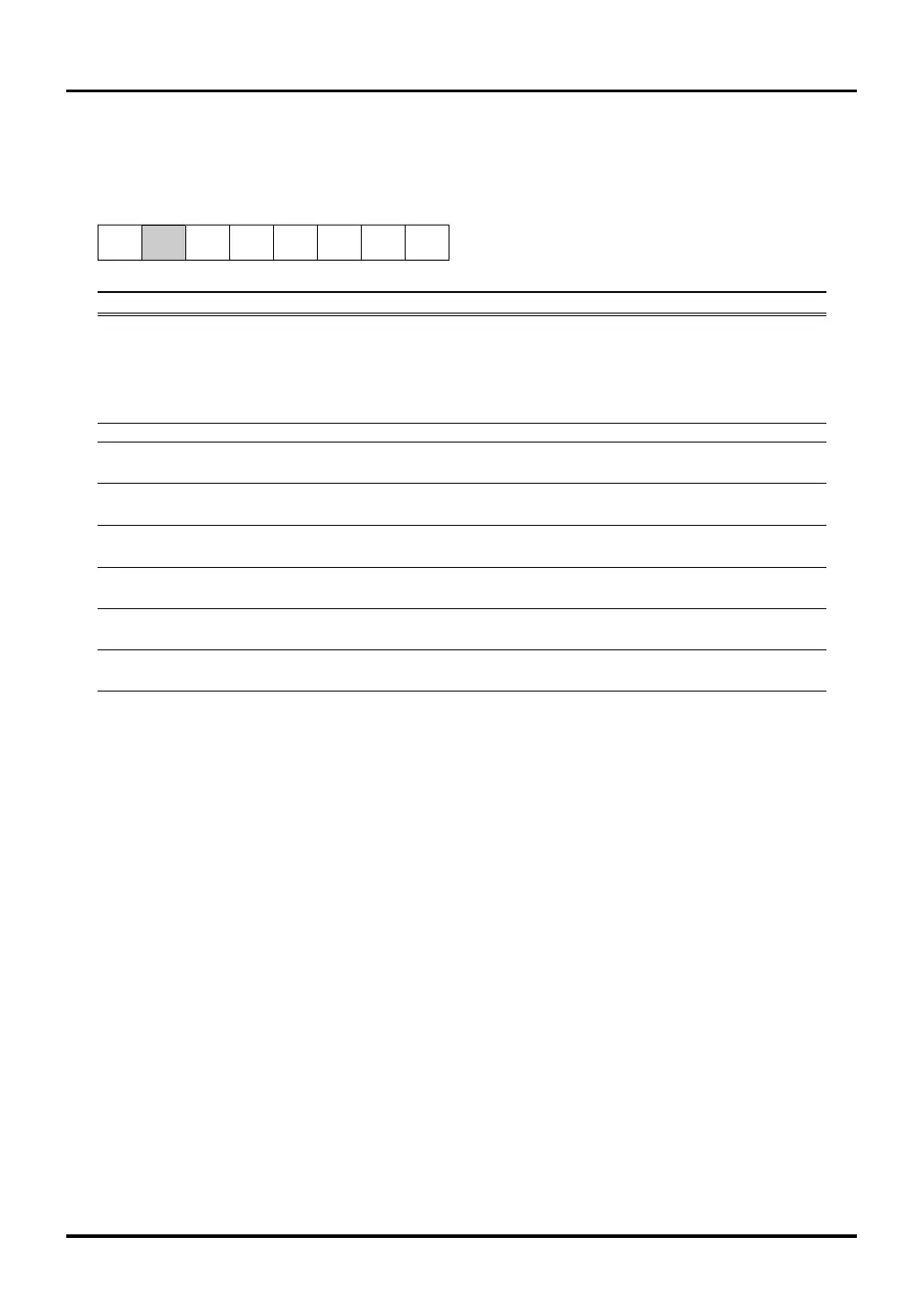

123456b7b0

ADSTRG0ADSTRG1

ADSSEL

ADSREQ ADSSTTADSSTPADSCMP

0 000100

<After reset: H’04>

b Bit Name Function R W

0 ADSTRG1 (Note 1) Bits 0 and 2 are used to select an A-D hardware trigger. R W

A-D hardware trigger select 1 bit b0 b2 A-D0 Converter A-D1 Converter

0 0 : Input event bus 2 Input event bus 2

0 1 : Input event bus 3 Input event bus 3

1 0 : Output event bus 3 TID1_udf/ovf

1 1 : TIN23S signal TIN23S signal

1 No function assigned. Fix to "0". 00

2 ADSTRG0 (Note 1) Bits 0 and 2 are used to select an A-D hardware trigger. R W

A-D hardware trigger select 0 bit (See the column for bit 0.)

3 ADSSEL 0: Software trigger R W

A-D conversion start trigger select bit 1: Hardware trigger (Note 2)

4 ADSREQ 0: A-D conversion interrupt request R W

Interrupt/DMA transfer request select bit 1: DMA transfer request

5 ADSCMP 0: A-D conversion/comparate in progress R –

A-D conversion/comparate completed bit 1: A-D conversion/comparate completed

6 ADSSTP 0: No operation 0 W

A-D conversion stop bit 1: Stop A-D conversion

7 ADSSTT 0: No operation 0 W

A-D conversion start bit 1:Start A-D conversion

Note 1: Two bits—A-D hardware trigger select 1 (bit 0) and A-D hardware trigger select 0 (bit 2)—are used to select an A-D

hardware trigger.

Note 2: During comparator mode, hardware triggers, if any selected, are ignored and operation is started by a software trigger.

A-D Single Mode Registers 0 are used to control operation of the A-D Converters during single mode (including

“Forcible single mode execution during scan mode”).

(1) ADSTRG (A-D Hardware Trigger Select) bits (Bits 0 and 2)

These bits select a hardware trigger when A-D conversion by the A-D Converter is to be started in hardware.

Select one from the following hardware trigger sources:

A-D0 Converter: Input event bus 2 A-D1 Converter: Input event bus 2

Input event bus 3 Input event bus 3

Output event bus 3 TID1 underflow/overflow

TIN23 edge select output TIN23 edge select output

The contents of these bits are ignored if a software trigger is selected by ADSSEL (A-D conversion start

trigger select bit).

Loading...

Loading...