9

DMAC

9-19

32180 Group User’s Manual (Rev.1.0)

9.2.3 DMA Source Address Registers

DMA0 Source Address Register (DM0SA) <Address: H’0080 0412>

DMA1 Source Address Register (DM1SA) <Address: H’0080 0422>

DMA2 Source Address Register (DM2SA) <Address: H’0080 0432>

DMA3 Source Address Register (DM3SA) <Address: H’0080 0442>

DMA4 Source Address Register (DM4SA) <Address: H’0080 0452>

DMA5 Source Address Register (DM5SA) <Address: H’0080 041A>

DMA6 Source Address Register (DM6SA) <Address: H’0080 042A>

DMA7 Source Address Register (DM7SA) <Address: H’0080 043A>

DMA8 Source Address Register (DM8SA) <Address: H’0080 044A>

DMA9 Source Address Register (DM9SA) <Address: H’0080 045A>

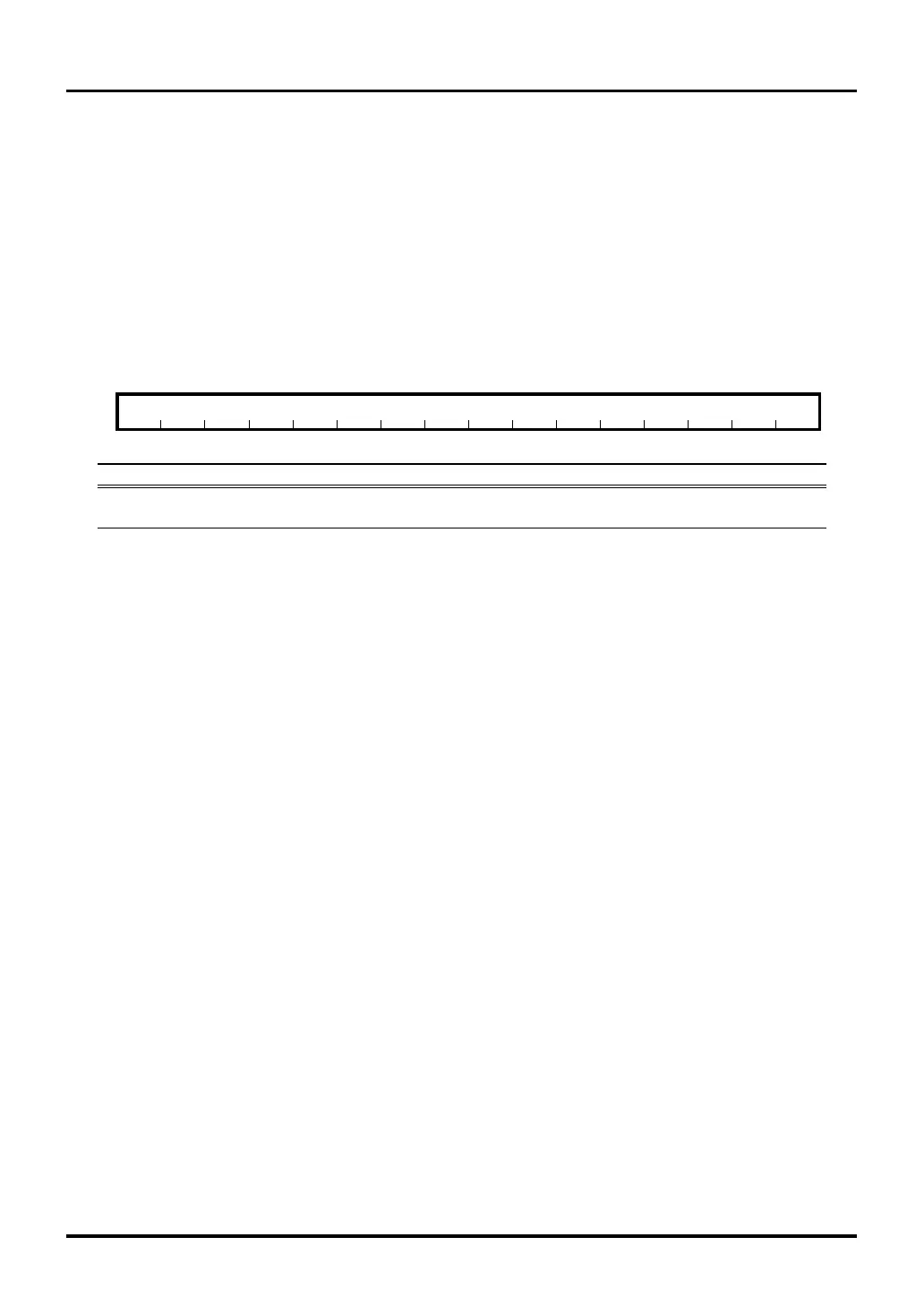

b01234567891011121314b15

DM0SA–DM9SA

????????????????

<After reset: Undefined>

b Bit Name Function R W

0–15 DM0SA–DMA9SA Source address bits A16–A31 R W

(A0–A15 are fixed to H’0080)

Note: • This register must always be accessed in halfwords.

The DMA Source Address Register is used to set the source address of DMA transfer in such a way that bit 0

and bit 5 correspond to A16 and A31, respectively. Because this register is comprised of a current register, the

values read from this register are always the current value.

When DMA transfer finishes (i.e., the Transfer Count Register underflows), the value in this register if “Address

fixed” is selected, is the same source address that was set in it before the DMA transfer began; if “Address

incremental” is selected, the value in this register is the last transfer address + 1 (for 8-bit transfer) or the last

transfer address + 2 (for 16-bit transfer).

The DMA Source Address Register must always be accessed in halfwords (16 bits) beginning with an even

address. If accessed in bytes, the value in this register is undefined.

(1) DM0SA–DM9SA (Source Address bits A16–A31)

Set this register to specify the source address of DMA transfer in the internal I/O or RAM space from the

address H’0080 0000 to the address H’0080 FFFF.

The 16 high-order source address bits (A0–A15) are always fixed to H’0080. Use this register to set the 16

low-order source address bits (with bit 0 corresponding to the source address A16, and bit 15 corresponding

to the source address A31).

9.2 DMAC Related Registers

Loading...

Loading...