12

12-30

Serial I/O

12.3 Transmit Operation in CSIO Mode

32180 Group User's Manual (Rev.1.0)

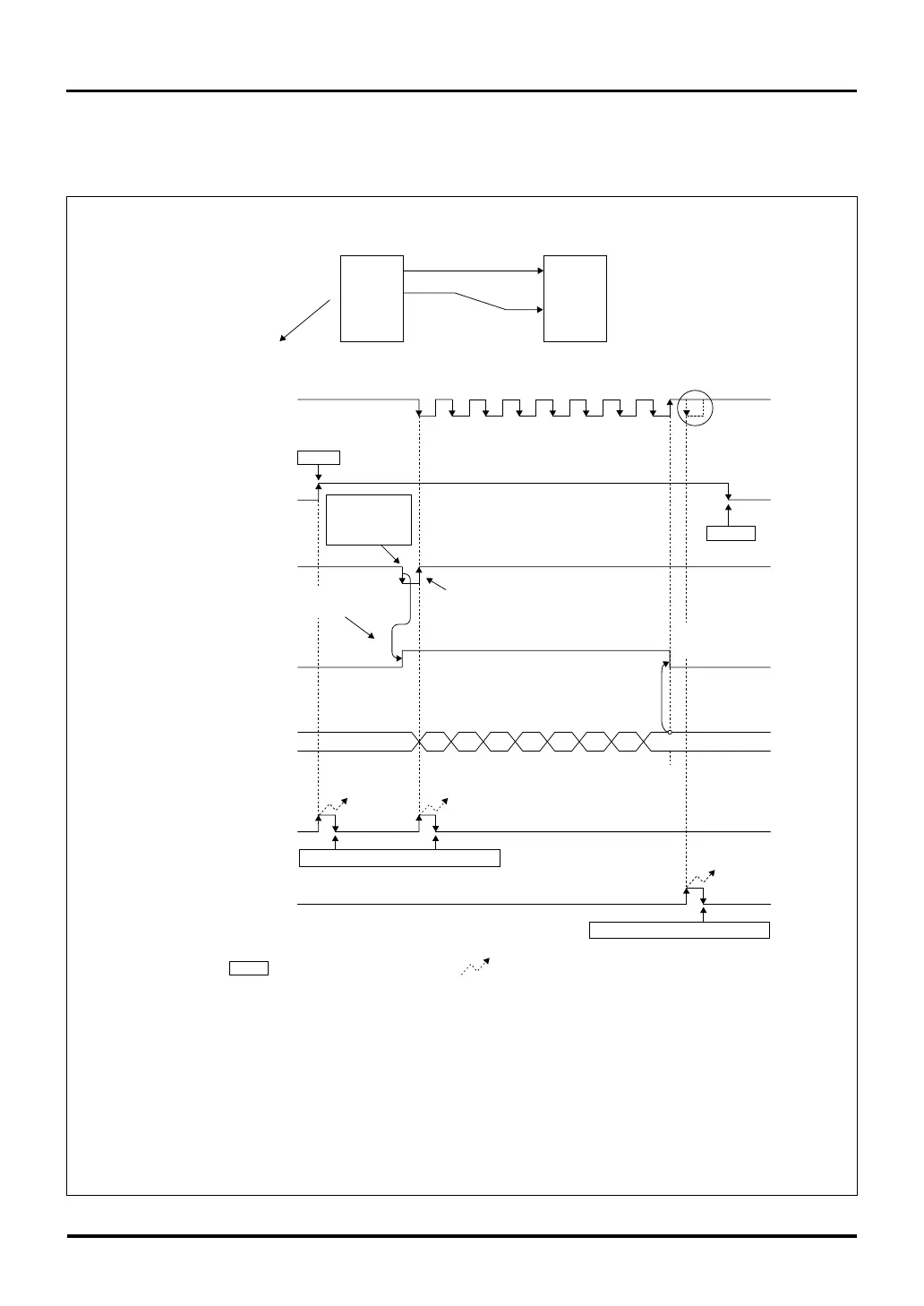

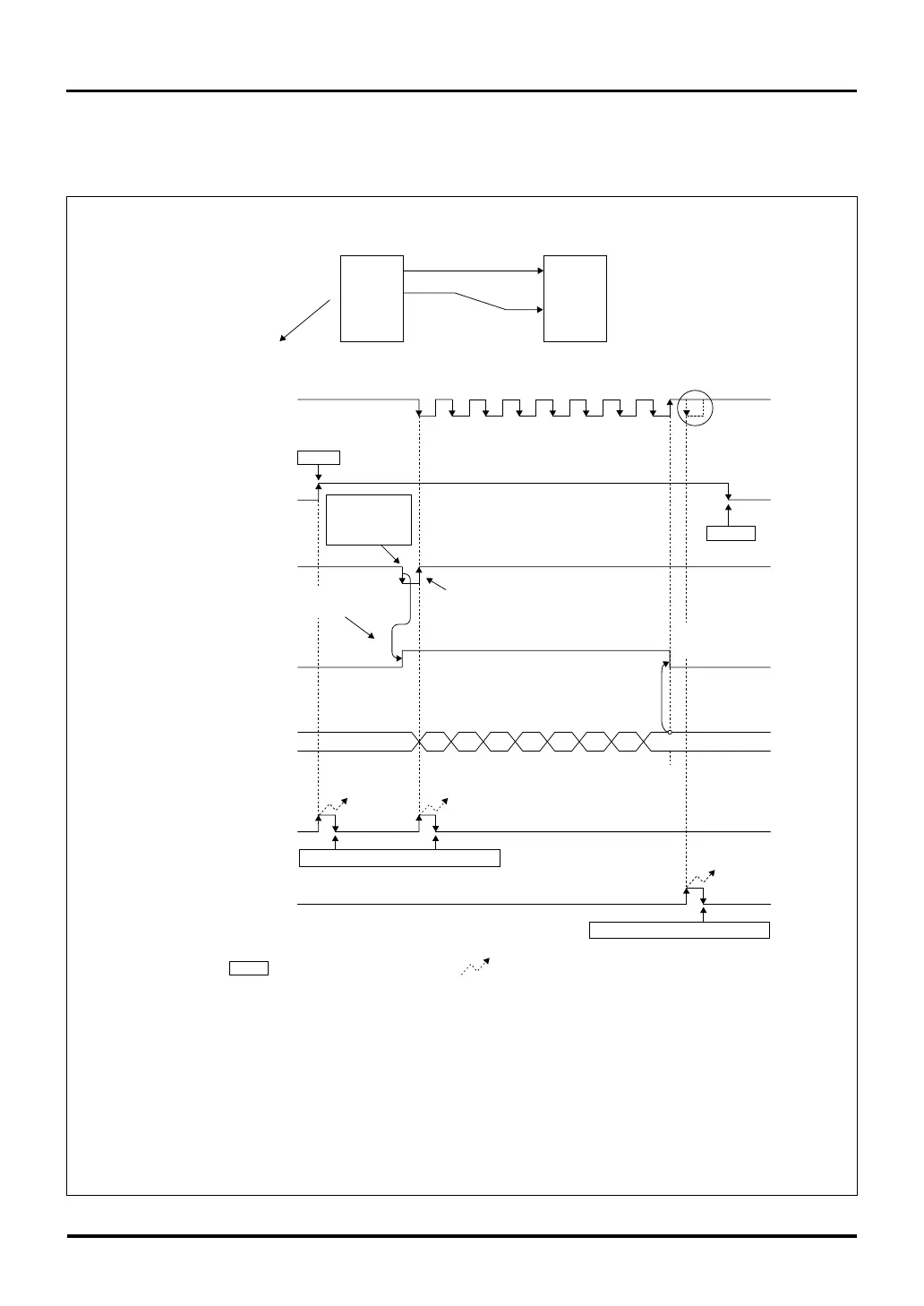

12.3.8 Example of CSIO Transmit Operation

The following shows a typical transmit operation in CSIO mode.

Figure 12.3.3 Example of CSIO Transmission (Transmitted Only Once)

Note 1: Changes of the Interrupt Controller's SIO Transmit Interrupt Control Register interrupt request bit

Note 2: When transmit buffer empty interrupt is enabled (DMA transfer can also be requested at the same time)

Note 3: When transmission finished interrupt is enable

Note 4: The Interrupt Controller's IVECT register is read or the SIO Transmit Interrupt Control Register interrupt

request bit cleared

Note 5: A transmit interrupt request is generated when transmission is enabled.

Note 6: Be aware that even after transmit data is written to the transmit buffer, a transmit interrupt request is generated when

the data is transferred from the transmit buffer to the transmit shift register and the transmit buffer is thereby emptied.

Note 7: A transmission finished interrupt request is generated by a falling edge of the internal transfer clock pulse

at which transmission of the transmit shift register data has finished or when the transmit enable bit is cleared.

Note 8: It is inhibited to select the transmission finished interrupt when an external clock is selected.

Internal clock selected

External clock selected

Set

Transmit enable bit

Transmit buffer empty bit

Transmit status bit

TXD

(When transmit buffer empty

interrupt is selected)

Transmit interrupt request

(Note 2) (Note 5)

Transmit interrupt request

(Note 2) (Note 6)

Interrupt request accepted (Note 4)

Set by a write to the

transmit buffer

Write to the

transmit buffer

register

Transmit clock

(SCLKO)

<CSIO on transmit side>

Cleared

Cleared by completion

of transmission

b7 b6 b5 b4 b3 b2 b1 b0

Content of the transmit buffer register

is transferred to the transmit shift register

: Interrupt request generated : Processing by software

<CSIO on transmit side>

<CSIO on receive side>

SCLKO

TXD

SCLKI

RXD

Transmit interrupt request

(Note 3) (Note 7)

Interrupt request accepted

(When transmission finished

interrupt is selected)(Note 8)

(Internal transfer clock)

SIO transmit interrupt request

(Note 1)

Loading...

Loading...