9

DMAC

9-33

32180 Group User’s Manual (Rev.1.0)

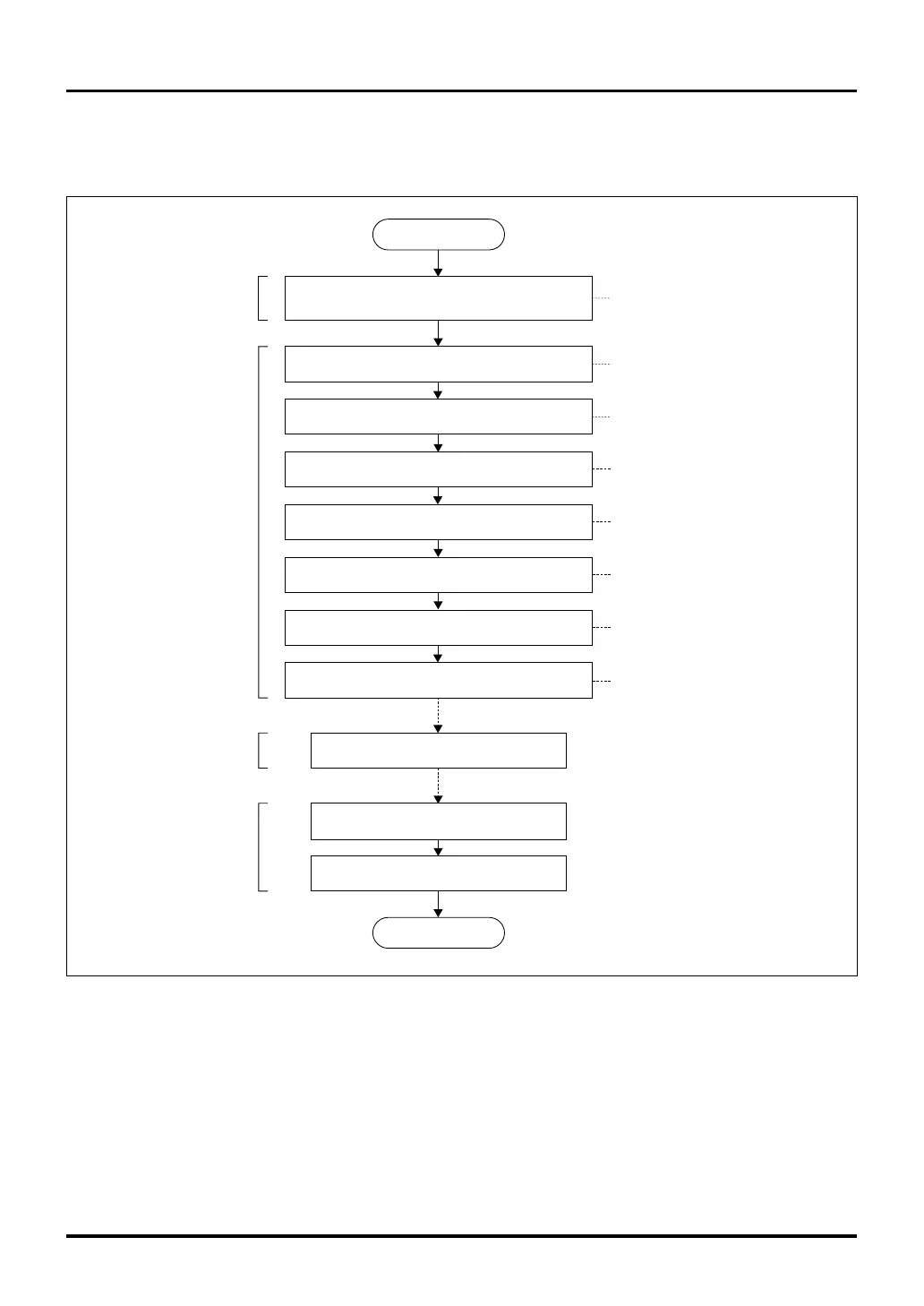

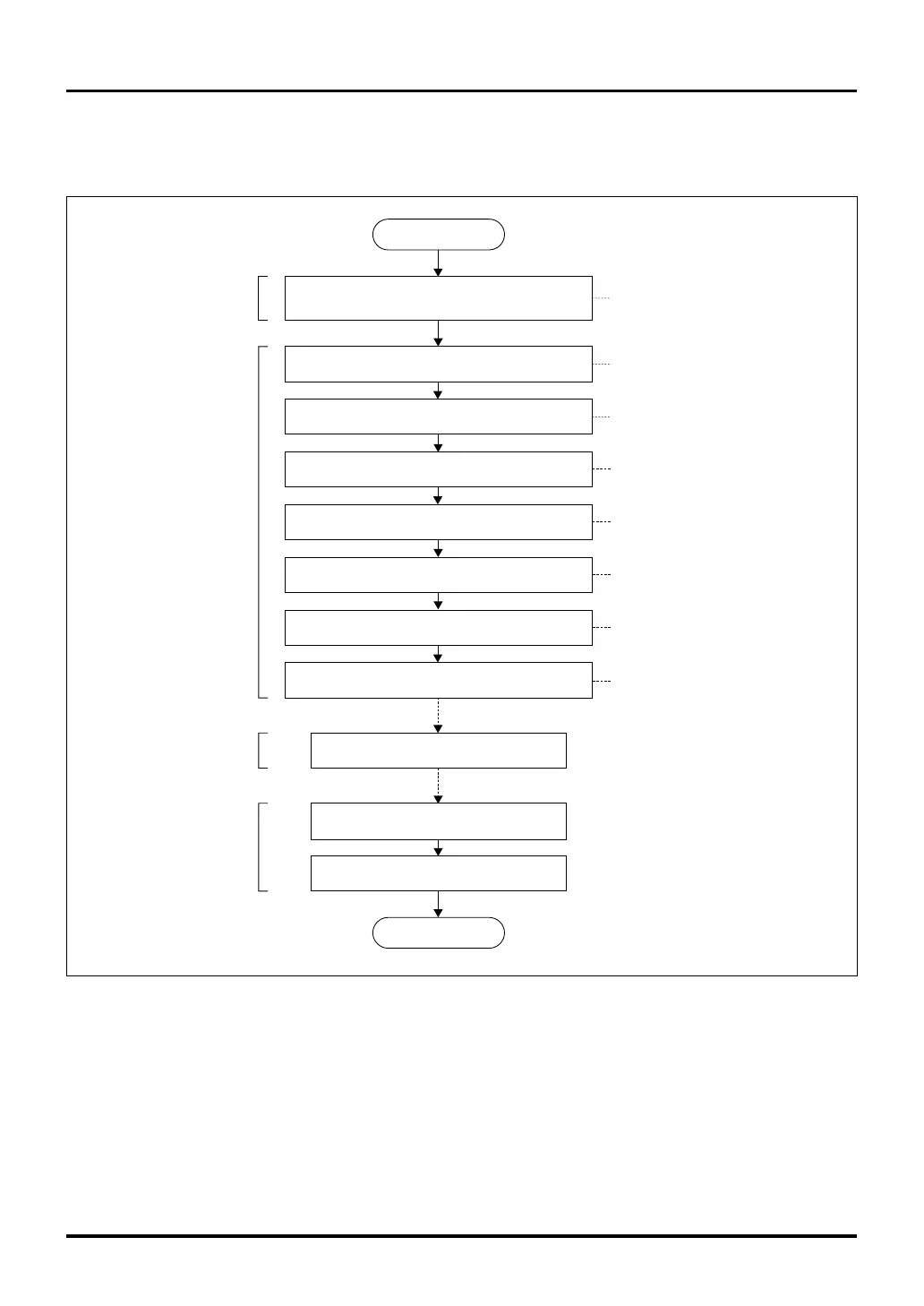

DMA transfer starts as requested by

internal peripheral I/O

DMA transfer

processing starts

Transfer count register underflows

Interrupt request generated

Set DMA0 Channel Control Register 0

Set DMA0-4 Interrupt Request Status Registers 0 and 1

Set DMA0 Channel Control Registers 0 and 1

Set DMA0 Source Address Register

Set DMA0 Destination Address Register

Set DMA0 Count Register

Setting

DMAC-related

registers

Starting DMA transfer

DMA transfer

completed

• Transfers disabled

• Interrupt request status

bits cleared

Set DMA0-4 Interrupt Request Mask Register

• Source address of transfer

• Destination address of transfer

• Number of times DMA transfer

is performed

• Transfer mode, request source,

transfer size, address direction

and transfer enable

DMA operation

completed

• Interrupt request enabled

Set the interrupt controller's

DMA0-4 Interrupt Control Register

• Interrupt priority level

Setting interrupt

controller-related

registers

Figure 9.3.1 Example of a DMA Transfer Processing Procedure

9.3.2 DMA Transfer Processing Procedure

Shown below is an example of how to control DMA transfer in cases when performing transfer on DMA channel 0.

9.3 Functional Description of the DMAC

Loading...

Loading...