11

11-34

A-D Converters

32180 Group User's Manual (Rev.1.0)

11.3.2 A-D Conversion by Successive Approximation Method

The A-D Converters use an A-D conversion start trigger (software or hardware) as they start A-D conversion.

Once A-D conversion begins, the following operation is automatically performed.

1. During single mode, A-D Single Mode Register 0’s A-D conversion/comparate completion bit is cleared to "0".

During scan mode, A-D Scan Mode Register 0’s A-D conversion completion bit is cleared to "0".

2. The content of the A-D Successive Approximation Register is cleared to H’0000.

3. The A-D Successive Approximation Register’s most significant bit (bit 6) is set to "1".

4. The comparison voltage, Vref (Note 1), is fed from the D-A Converter into the comparator.

5. The comparison voltage, Vref, and the analog input voltage, VIN, are compared, with the comparison result

stored in bit 6.

If Vref < VIN, then bit 6 = "1"

If Vref > VIN, then bit 6 = "0"

6. Operations in 3 through 5 above are executed for all other bits from bit 7 to bit 15.

7. The value stored in the A-D Successive Approximation Register by the time comparison for bit 15 has finished

is held in it as the A-D conversion result.

11.3 Functional Description of A-D Converters

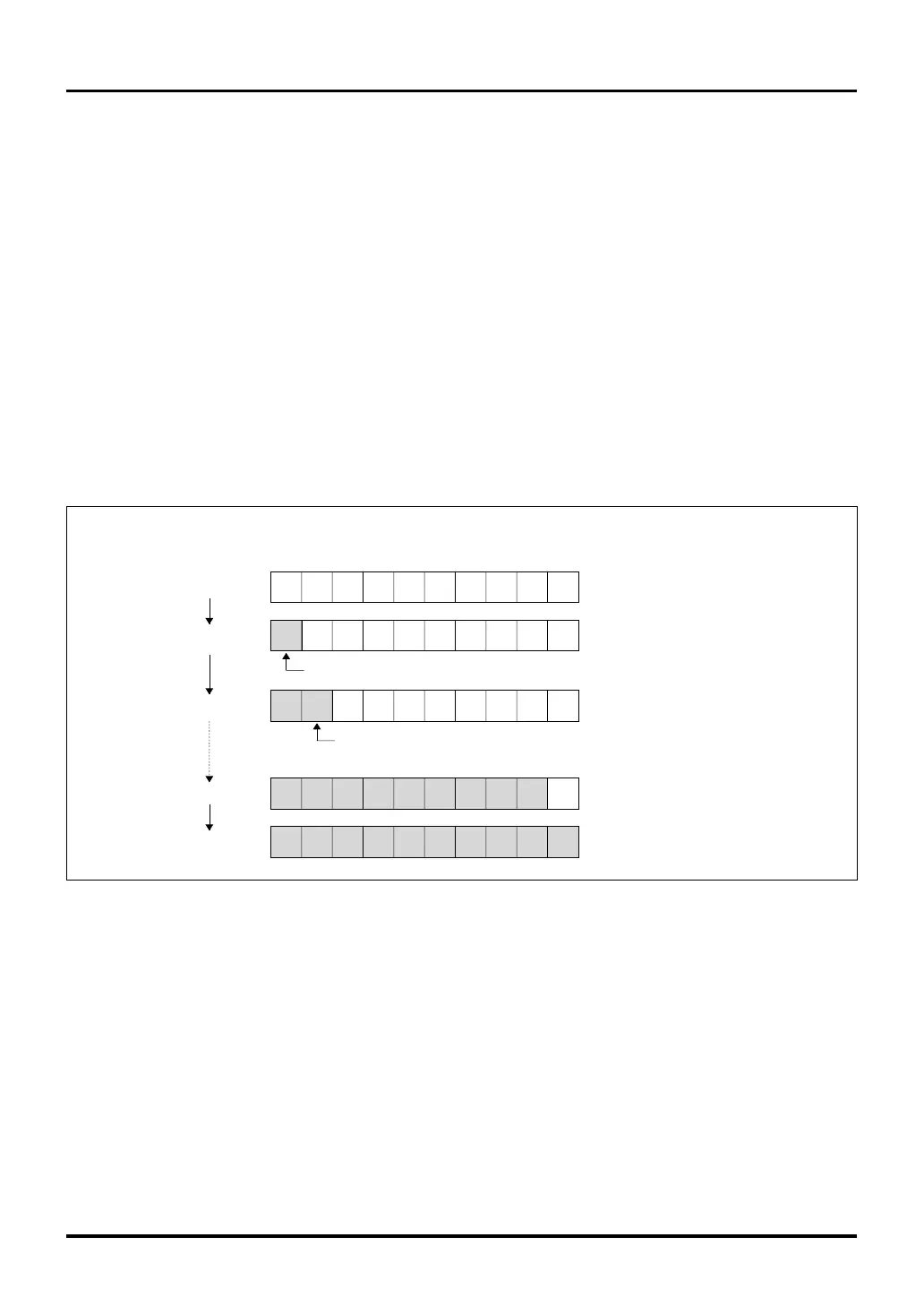

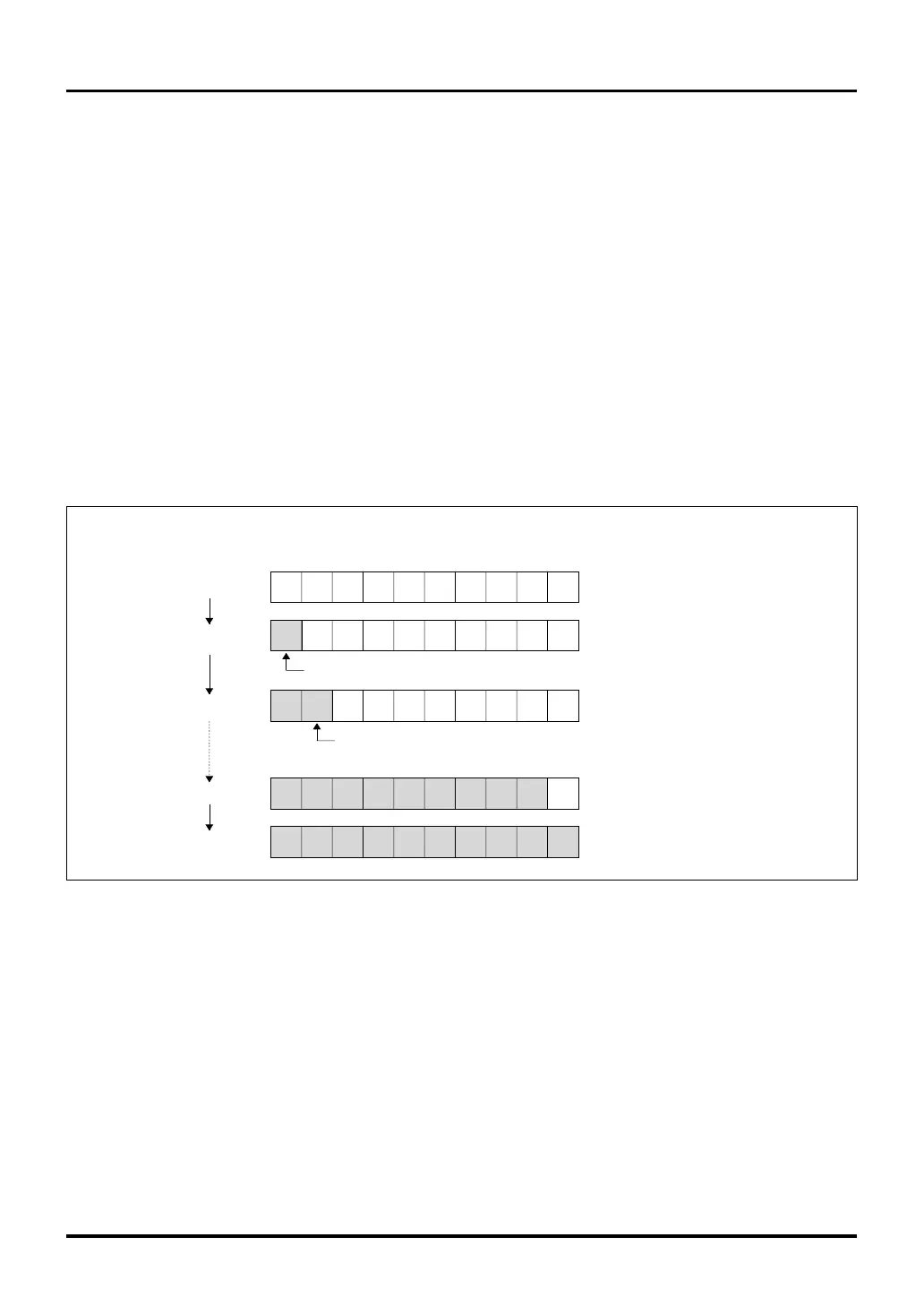

1st comparison

b6 7 8 9 1011121314b15

100000000

0

n910000000

0

n9n81000000

0

n9 n8 n7 n6 n5 n4 n3 n2 n1

1

2nd comparison

3rd comparison

0th comparison

Conversion

p

n9 n8 n7 n6 n5 n4 n3 n2 n1 n0

Result of 1st comparison

Result of 2nd comparison

If Vref > VIN, then nX = 0

If Vref < VIN, then nX = 1

A-D Successive Approximation Register (ADiSAR) i = 0, 1

Figure 11.3.2 Changes of the A-D Successive Approximation Register during A-D Convert Operation

Note 1: The comparison voltage, Vref (the voltage fed from the D-A Converter into the comparator), is

determined according to changes of the A-D Successive Approximation Register content. Shown

below are the equations used to calculate the comparison voltage, Vref.

• If the A-D Successive Approximation Register content = 0

Vref [V] = 0

• If the A-D Successive Approximation Register content = 1 to 1,023

Vref [V] = (reference voltage VREF / 1,024) × (A-D Successive Approximation Register content – 0.5)

Loading...

Loading...