4

4-19

EIT

32180 Group User’s Manual (Rev.1.0)

4.10 Trap Processing

(4) Branching to the EIT vector entry

The CPU branches to the addresses H’0000 0040–H’0000 007C in the user space. This is the last operation

performed in hardware preprocessing.

(5) Jumping from the EIT vector entry to the user-created handler

The CPU executes the BRA instruction written by the user at the addresses H’0000 0040–H’0000 007C of

the EIT vector entry to jump to the start address of the user-created handler. At the beginning of the user-

created EIT handler, first save the BPC and PSW registers and the necessary general-purpose registers to

the stack.

(6) Returning from the EIT handler

At the end of the EIT handler, restore the general-purpose registers and the BPC and PSW registers from

the stack and execute the RTE instruction. When the RTE instruction is executed, hardware postprocessing

is automatically performed. At this time, the CPU restarts from the next word-boundary instruction including

the instruction that generates a trap (see Figure 4.10.1).

4.11 EIT Priority Levels

The table below lists the priority levels of EIT events. When two or more EITs occur simultaneously, the event with

the highest priority is accepted first.

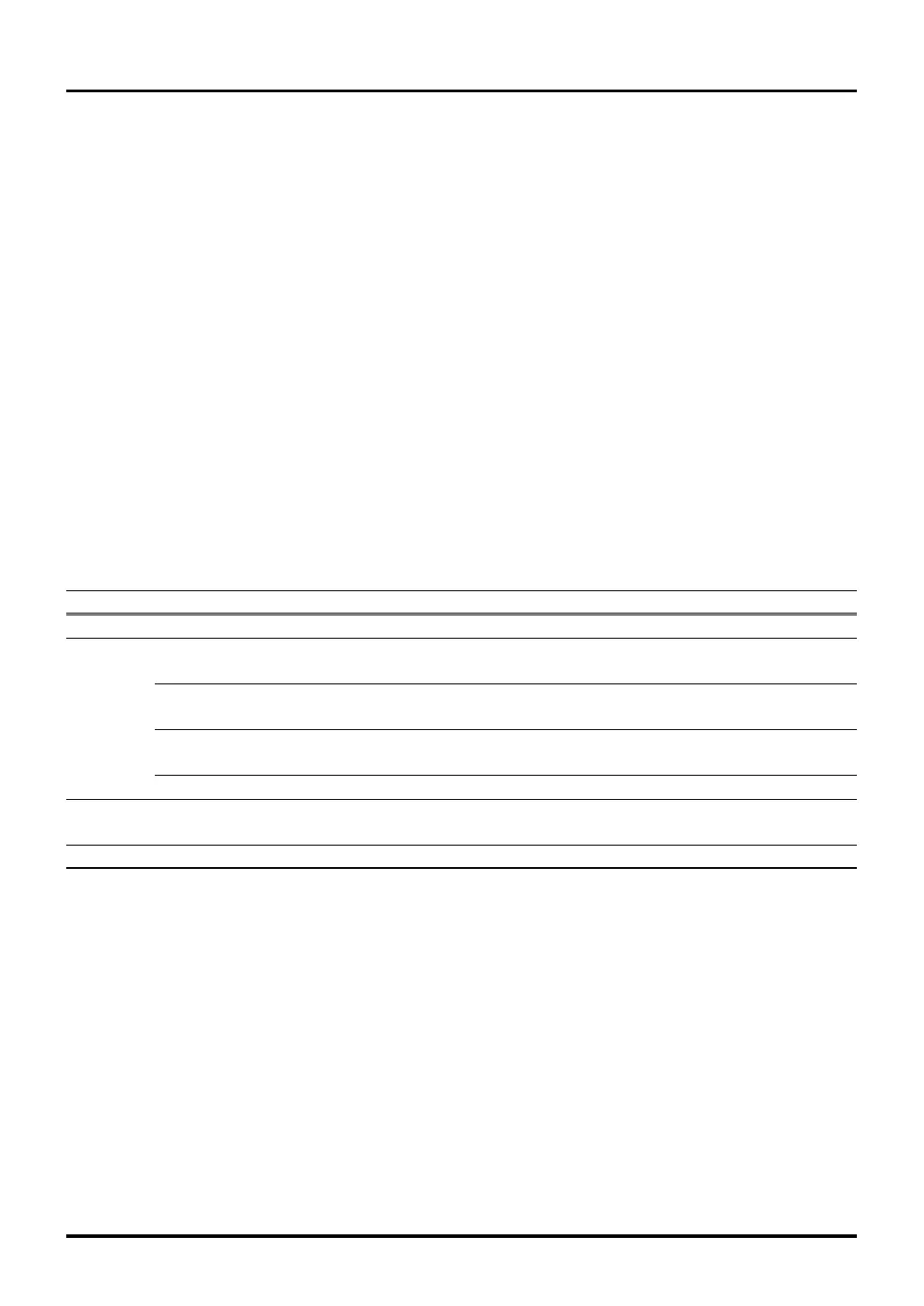

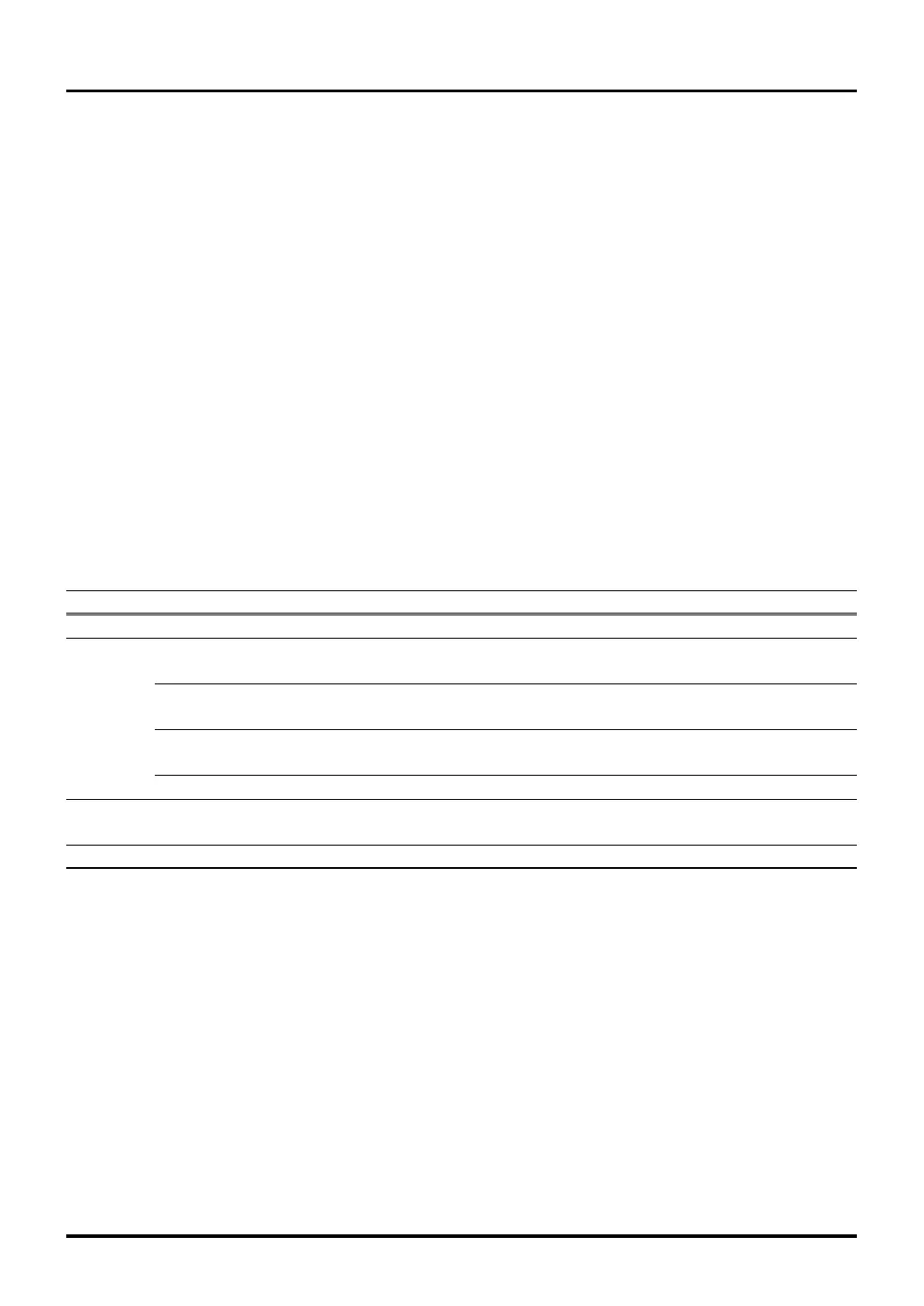

Table 4.11.1 Priority of EIT Events and How Returned from EIT

Priority EIT Event Type of Processing Values Set in BPC Register

1 (Highest) Reset Interrupt (RI) Instruction processing-aborted type Undefined

2 Address Exception (AE) Instruction processing-canceled type PC of the instruction that

generated AE

Reserved Instruction Instruction processing-canceled type PC of the instruction that

Exception (RIE) generated AE

Floating-Point Exception Instruction processing-completed type PC of the instruction that

(FPE) generated FPE + 4

Trap (TRAP) Instruction processing-completed type TRAP instruction + 4

3 System Break Interrupt Instruction processing-completed type PC of the next instruction

(SBI)

4 External Interrupt (EI) Instruction processing-completed type PC of the next instruction

Note that for External Interrupt (EI), the priority levels of interrupt requests from each peripheral I/O are set by the

microcomputer’s internal interrupt controller. For details, see Chapter 5, “Interrupt Controller.”

Loading...

Loading...