12

12-45

Serial I/O

12.6 Transmit Operation in UART Mode

32180 Group User's Manual (Rev.1.0)

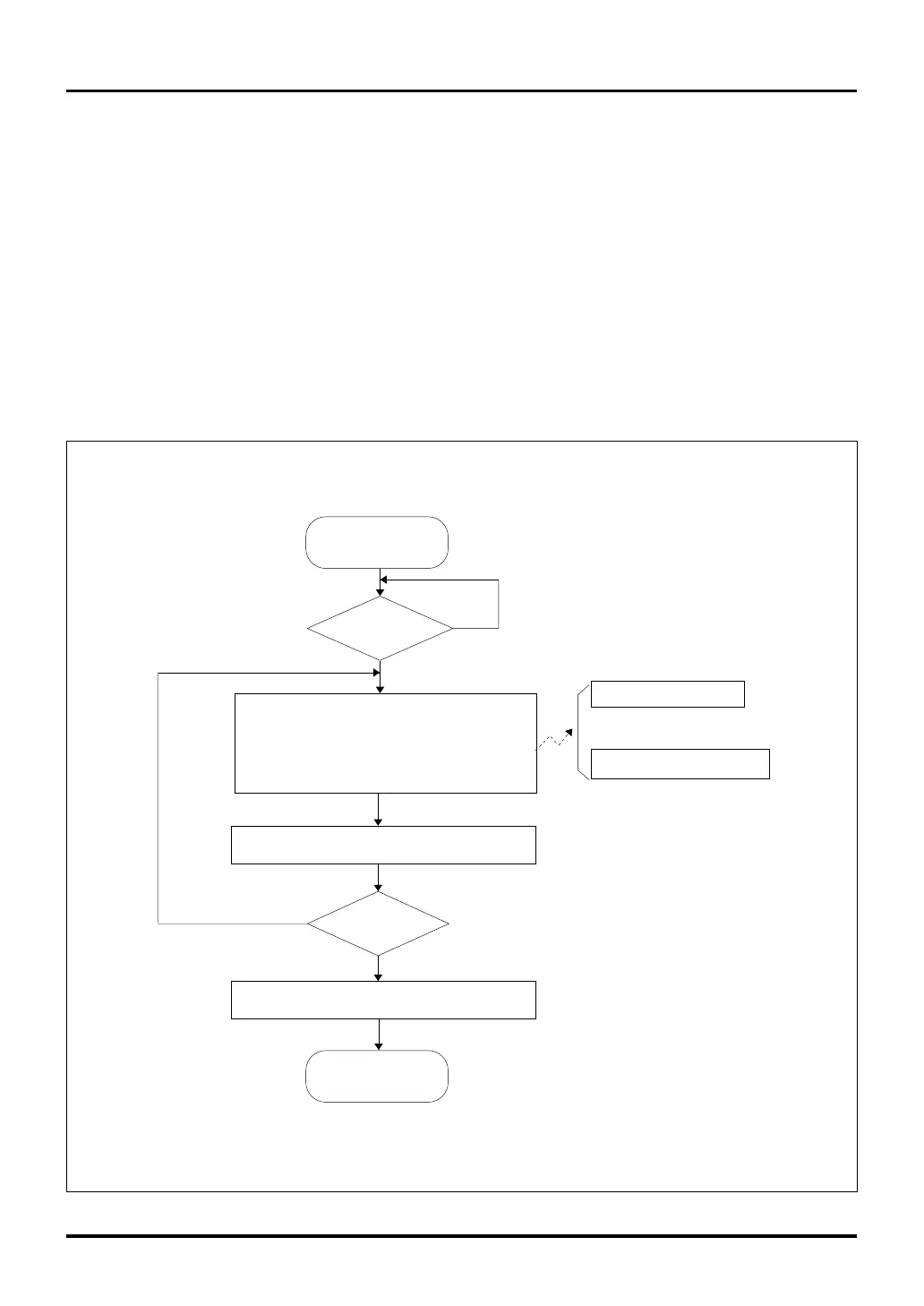

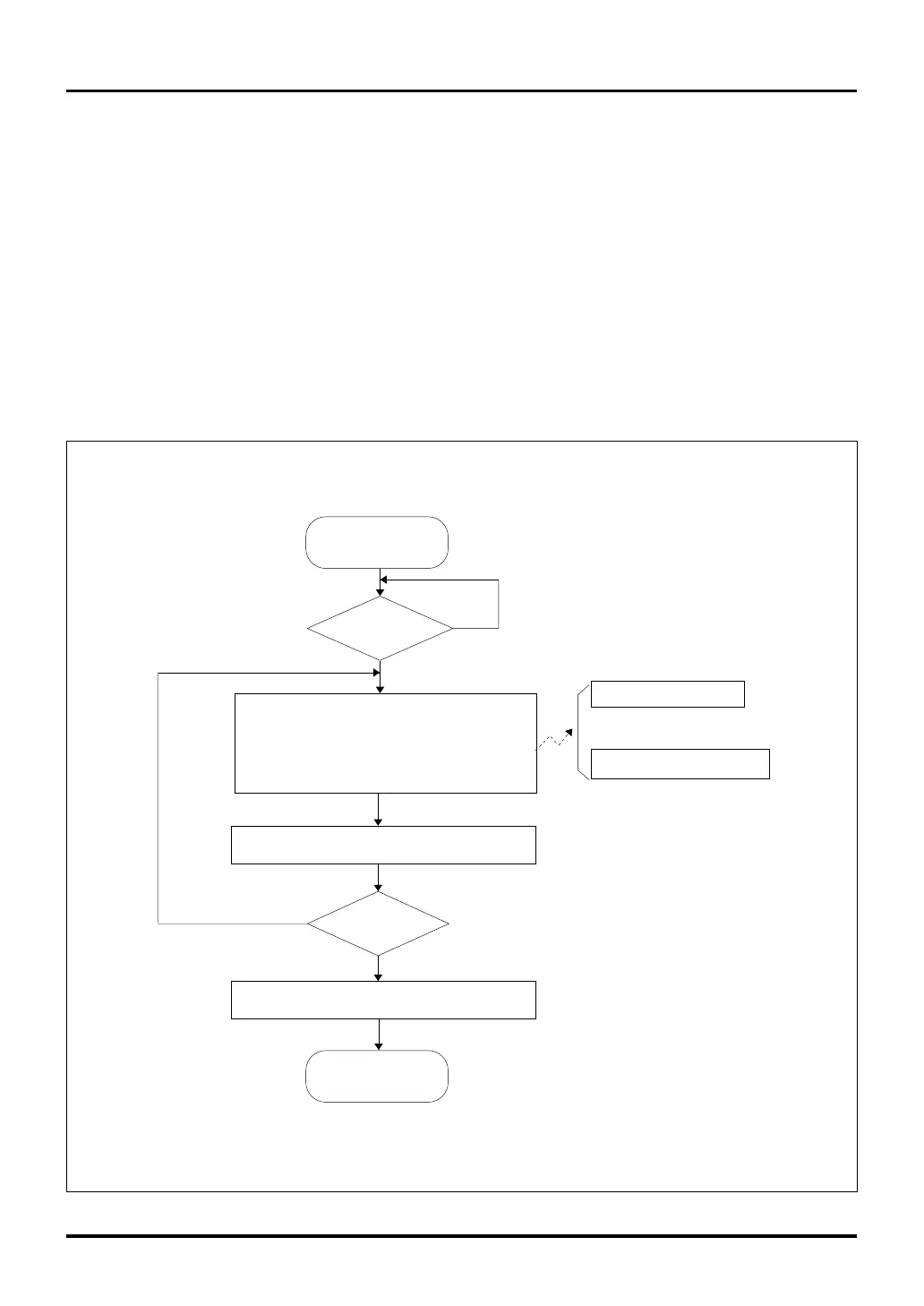

Figure 12.6.4 Transmit Operation during UART Mode (Hardware Processing)

The following processing is automatically performed in hardware.

•

Transfer the content of the transmit buffer

to the transmit shift register

•

Set the transmit buffer empty bit to "1"

Transmit DMA transfer request

Transmit interrupt request

Transmit data

Y (Successive transmission)

Transmit conditions

met ?

Transmit conditions

met ?

Clear the transmit status bit to "0"

Y

N

N

(Note 1)

Note 1: This applies when the transmit interrupt was enabled using the SIO Interrupt Request Enable Register

after selecting the transmit buffer empty interrupt with the SIO Interrupt Request Source Select Register.

End of UART

transmit operation

UART transmit

operation starts

(2) Transmission finished interrupt

If the transmission finished interrupt was selected using the SIO Interrupt Request Source Select Register, a

transmission finished interrupt request is generated when data in the transmit shift register has all been

transmitted.

The SIO Interrupt Request Enable Register and the Interrupt Controller (ICU) must be set before these transmit

interrupts can be used.

12.6.8 Transmit DMA Transfer Request

When data has been transferred from the transmit buffer register to the transmit shift register, a transmit DMA

transfer request for the corresponding SIO channel is output to the DMAC. A transmit DMA transfer request is

also output when the TEN (Transmit Enable) bit is set to "1" (disabled → enabled).

The DMAC must be set before DMA transfers can be used during data transmission.

Loading...

Loading...