12

12-54

SERIAL I/O

12.7 Receive Operation in UART Mode

32180 Group User's Manual (Rev.1.0)

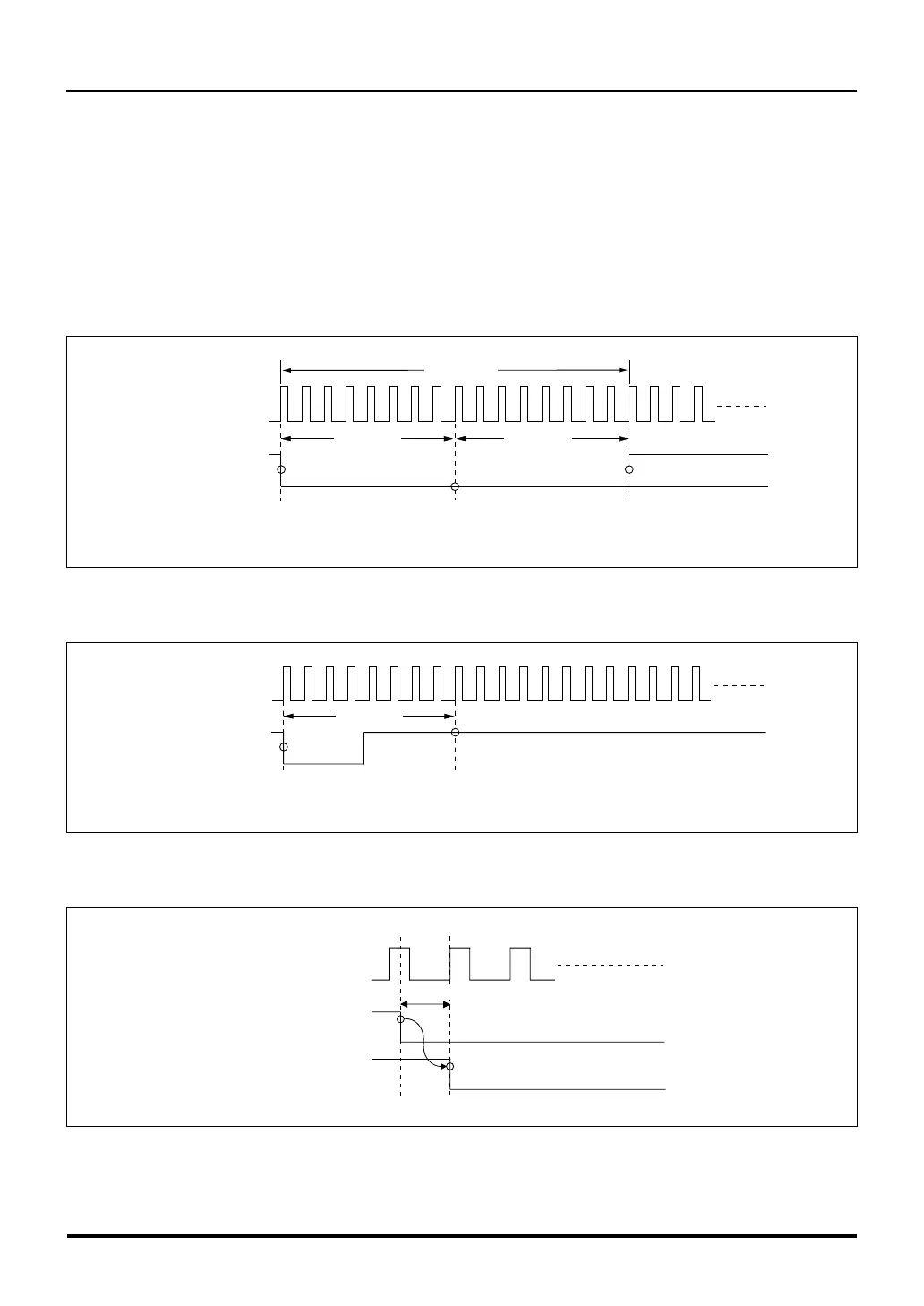

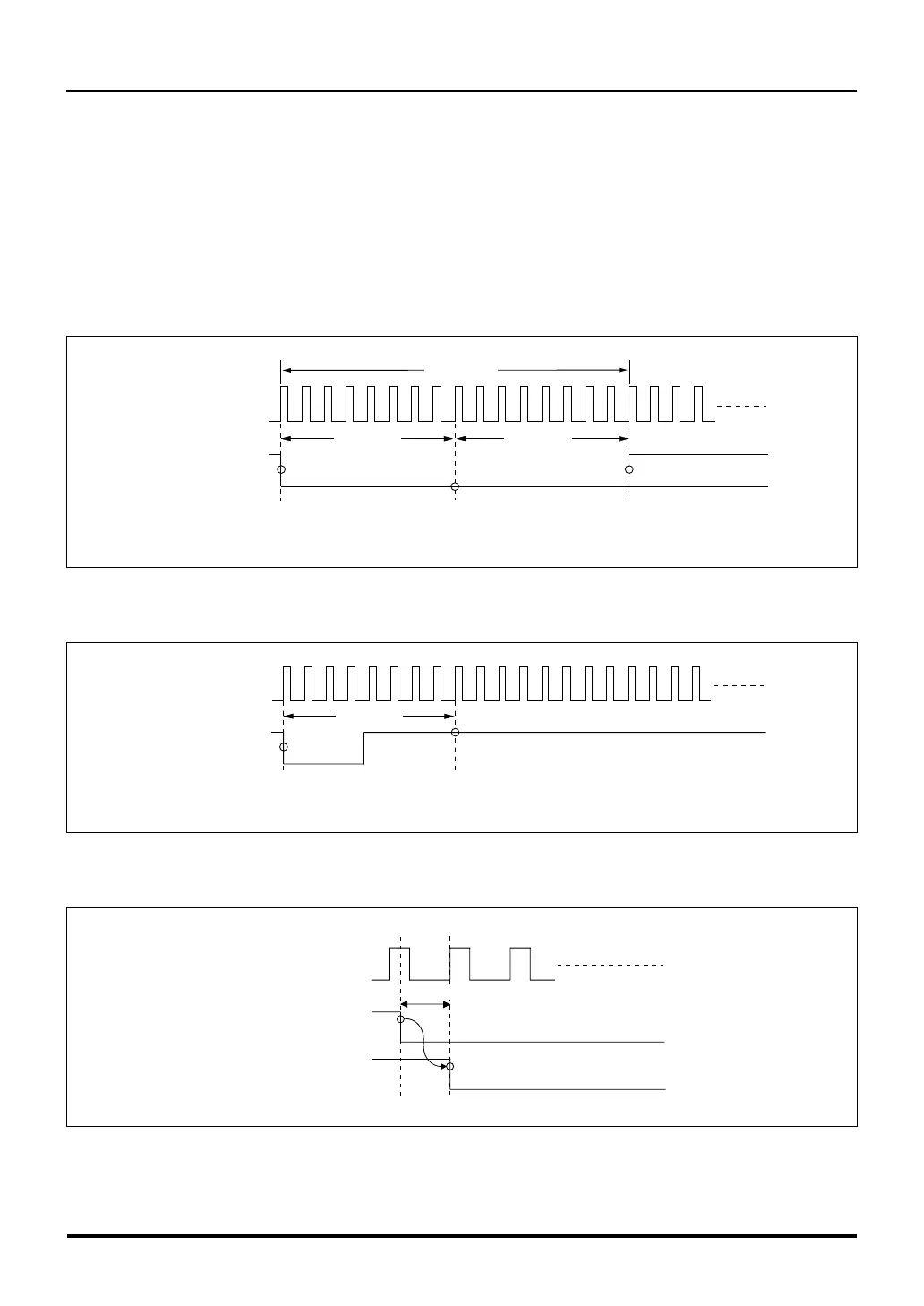

Figure 12.7.7 Delay in Receive Timing

12.7.5 Start Bit Detection during UART Reception

The start bit is sampled synchronously with the internal BRG output. If the received signal remains low for 8

BRG output cycles after the falling edge of the start bit, the CPU recognizes that part of the received signal as

the start bit and starts latching the received data another 8 cycles after that, beginning with the LSB (first bit). If

some sampled part of the received signal is high before being determined to be the start bit, the CPU starts

hunting the falling edge of the received signal again. Because the start bit is sampled synchronously with the

internal BRG output, there is a delay equivalent to one BRG output cycle at maximum. The subsequent received

data is latched into the internal circuit with that delayed timing.

Figure 12.7.5 Start Bit Detection

Figure 12.7.6 Example of an Invalid Start Bit (Not Received)

Internal BRG output

RXD

LSB data

16 cycles

8 cycles 8 cycles

Note: • This diagram does not show detailed timing information.

Internal BRG output

RXD

8 cycles

Note: • This diagram does not show detailed timing information.

Internal RXD

Internal BRG output

RXD

Delay equivalent to one BRG output cycle at maximum

Loading...

Loading...