4

4-17

EIT

32180 Group User’s Manual (Rev.1.0)

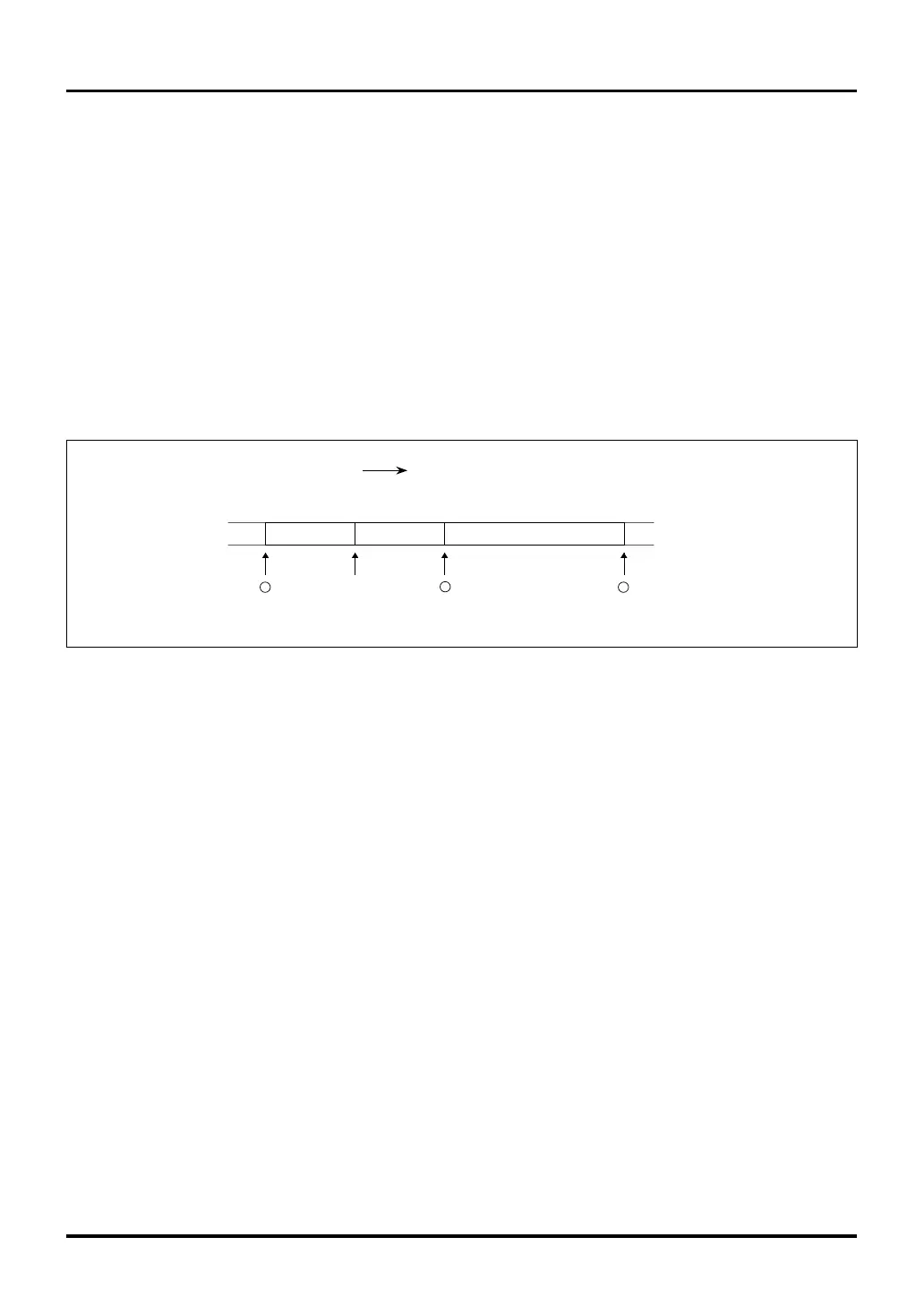

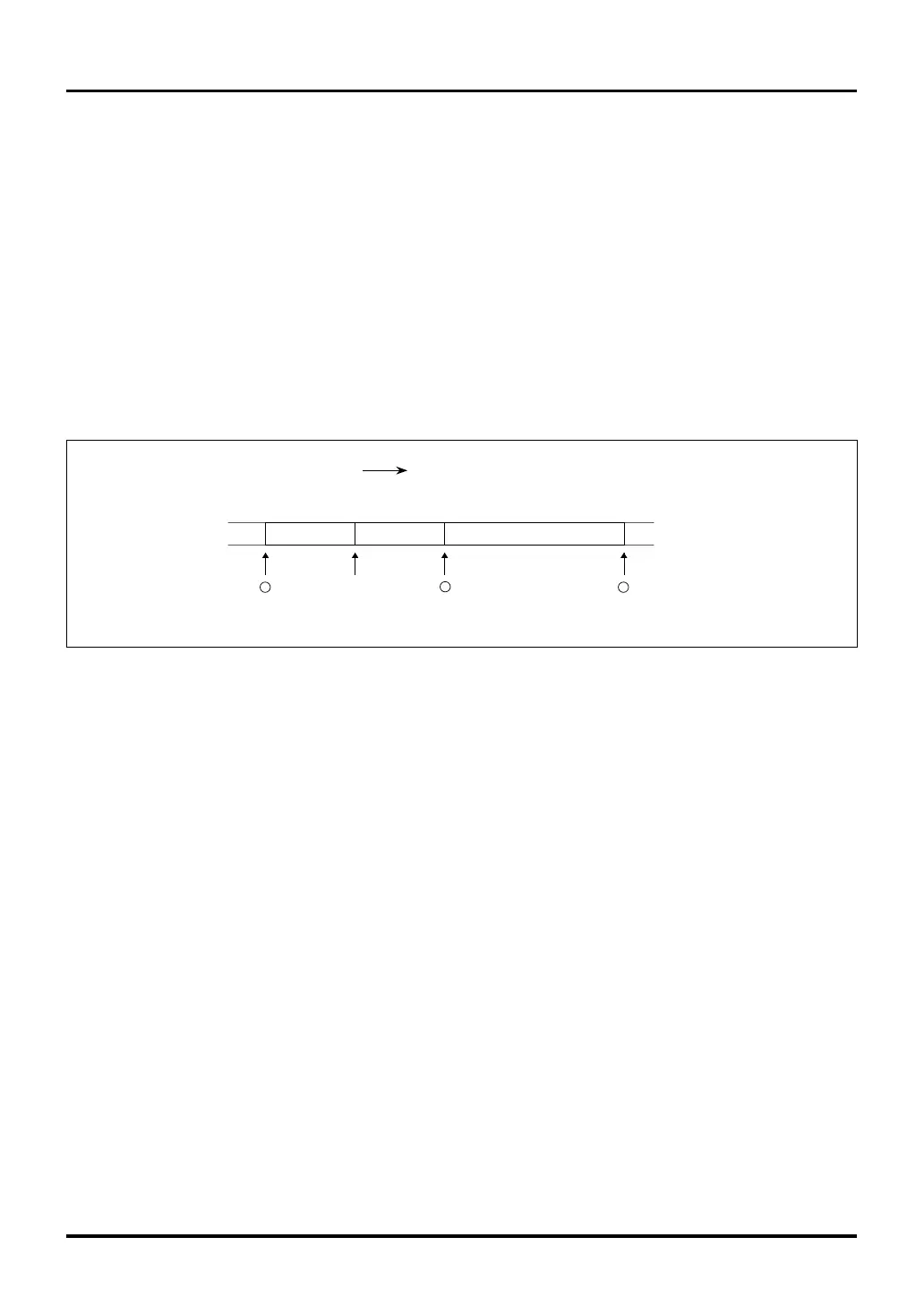

Figure 4.9.2 Timing at Which External Interrupt (EI) is Accepted

[EIT Processing]

(1) Saving SM, IE and C bits

The PSW register’s SM, IE and C bits are saved to the respective backup bits: BSM, BIE and BC.

BSM ← SM

BIE ← IE

BC ← C

(2) Updating SM, IE and C bits

The PSW register’s SM, IE and C bits are updated as shown below.

SM ← 0

IE ← 0

C ← 0

(3) Saving the PC

The content of the PC register (always on word boundary) is saved to the BPC register.

(4) Branching to the EIT vector entry

The CPU branches to the address H’0000 0080 in the user space. However, when operating in flash E/W enable

mode, the CPU goes to the beginning of the internal RAM (address H’0080 4000). (For details, see Section 6.5,

“Programming the Internal Flash Memory.”) This is the last operation performed in hardware preprocessing.

(5) Jumping from the EIT vector entry to the user-created handler

The CPU executes the BRA instruction written by the user at the address H’0000 0080 of the EIT vector

entry to jump to the start address of the user-created handler. At the beginning of the user-created EIT

handler, first save the BPC and PSW registers and the necessary general-purpose registers to the stack.

Also, save the accumulator and FPSR register as necessary.

4.9.3 External Interrupt (EI)

An external interrupt is generated upon an interrupt request which is output by the microcomputer’s internal

interrupt controller. The interrupt controller manages interrupt requests by assigning each one of seven priority

levels. For details, see Chapter 5, “Interrupt Controller.” For details about the interrupt request sources, see each

section in which the relevant internal peripheral I/O is described.

[Occurrence Conditions]

External interrupts are managed based on interrupt requests from each internal peripheral I/O by the

microcomputer’s internal interrupt controller, and are sent to the CPU via the interrupt controller. The CPU checks

these interrupt requests at a break in instructions residing on word boundaries, and when an interrupt request is

detected and the PSW register IE flag = "1", accepts it as an external interrupt.

In no case will an external interrupt be activated immediately after executing a 16-bit instruction that starts from

a word boundary. (For 16-bit branch instructions, however, the interrupt is accepted immediately after branching.)

4.9 Interrupt Processing

16-bit instruction

Order in which instructions are executed

32-bit instruction

Address 1000 Address 1002 Address 1004 Address 1008

Interrupt may

be accepted

×

Interrupt cannot

be accepted

16-bit instruction

Interrupt may

be accepted

Interrupt may

be accepted

Loading...

Loading...