15

15-4

EXTERNAL BUS INTERFACE

32180 Group User’s Manual (Rev.1.0)

15.2 External Bus Interface Related Registers

The following describes the external bus interface related registers.

15.2.1 Port Operation Mode Registers

Ports P0–P4 (except P41–P43) and P224–P227 are switched for external access signal pins during external

extension mode when so set by the corresponding Operation Mode Register. During processor mode, these

ports always function as external access signal pins.

During external extension mode, these pins are switched for port after reset. Therefore, by switching the pin

functions for only those pins that are needed for external access, the remaining pins can be used as port.

Ports P70–P73 can be switched for external access signal pins at any time irrespective of the CPU operation

mode. Ports P41–P43 always function as external access signal pins during external extension and processor

modes.

P0 Operation Mode Register (P0MOD) <Address: H’0080 0740>

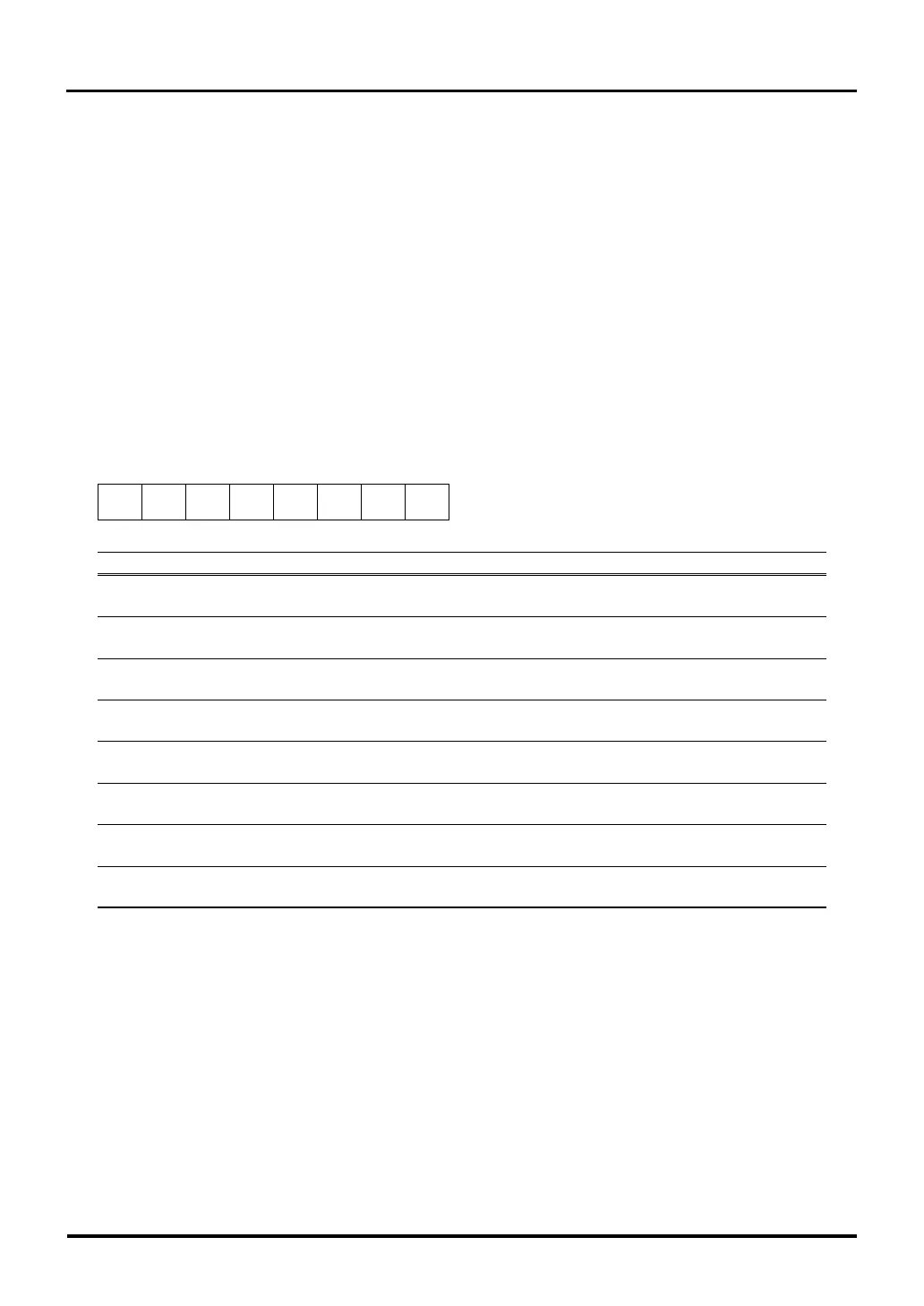

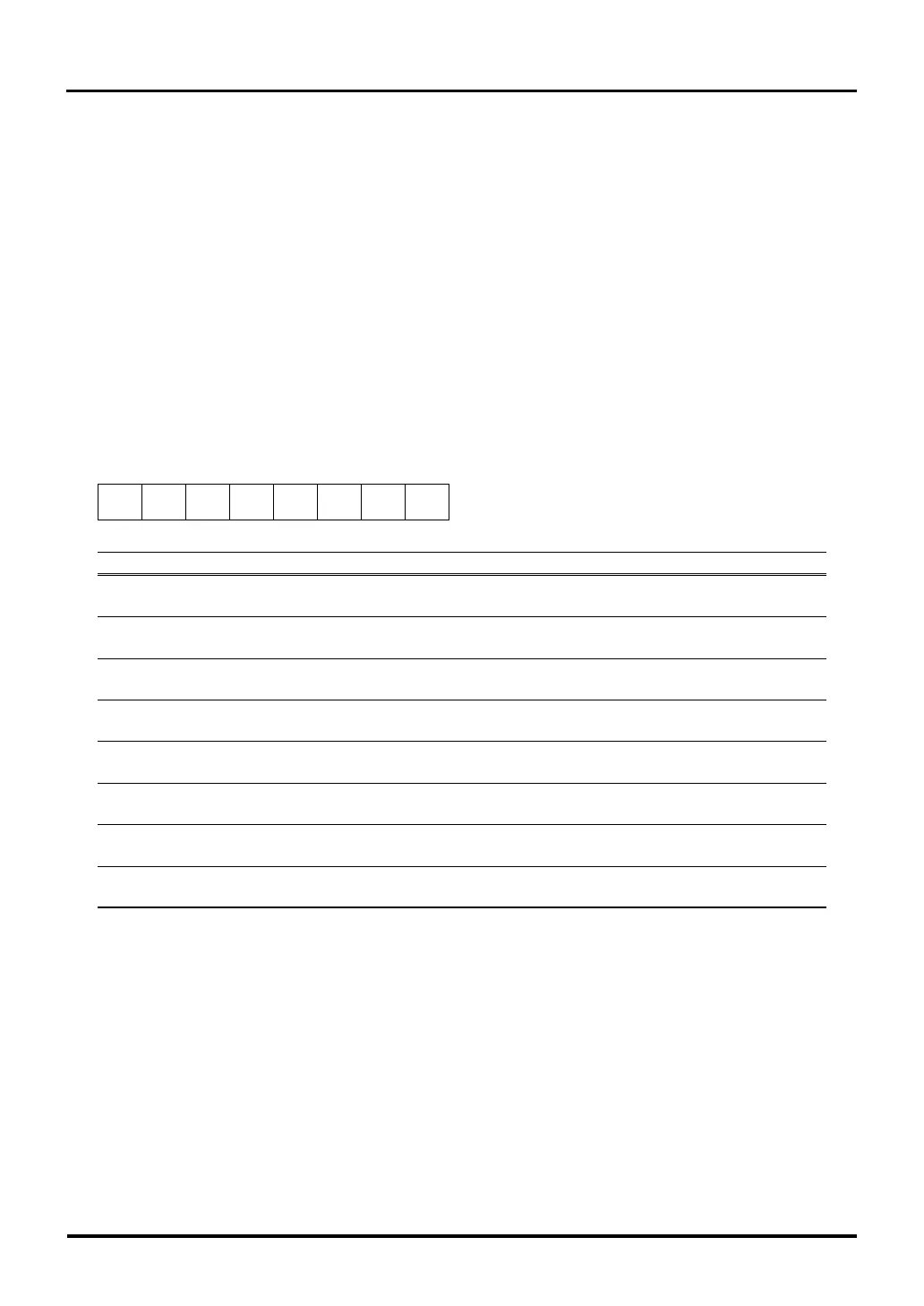

123456b7b0

P00MD P01MD P02MD P03MD P04MD P05MD P06MD P07MD

00000000

<After reset: H’00>

b Bit Name Function R W

0 P00MD 0: P00 R W

Port P00 operation mode bit 1: DB0

1 P01MD 0: P01 R W

Port P01 operation mode bit 1: DB1

2 P02MD 0: P02 R W

Port P02 operation mode bit 1: DB2

3 P03MD 0: P03 R W

Port P03 operation mode bit 1: DB3

4 P04MD 0: P04 R W

Port P04 operation mode bit 1: DB4

5 P05MD 0: P05 R W

Port P05 operation mode bit 1: DB5

6 P06MD 0: P06 R W

Port P06 operation mode bit 1: DB6

7 P07MD 0: P07 R W

Port P07 operation mode bit 1: DB7

Note: • Settings of the P0 Operation Mode Register are effective only when the CPU is operating in external extension mode.

15.2 External Bus Interface Related Registers

Loading...

Loading...