12

12-14

Serial I/O

12.2 Serial I/O Related Registers

32180 Group User's Manual (Rev.1.0)

12.2.2 SIO Transmit Control Registers

SIO0 Transmit Control Register (S0TCNT) <Address: H'0080 0110>

SIO1 Transmit Control Register (S1TCNT) <Address: H'0080 0120>

SIO2 Transmit Control Register (S2TCNT) <Address: H'0080 0130>

SIO3 Transmit Control Register (S3TCNT) <Address: H'0080 0140>

SIO4 Transmit Control Register (S4TCNT) <Address: H'0080 0A10>

SIO5 Transmit Control Register (S5TCNT) <Address: H'0080 0A20>

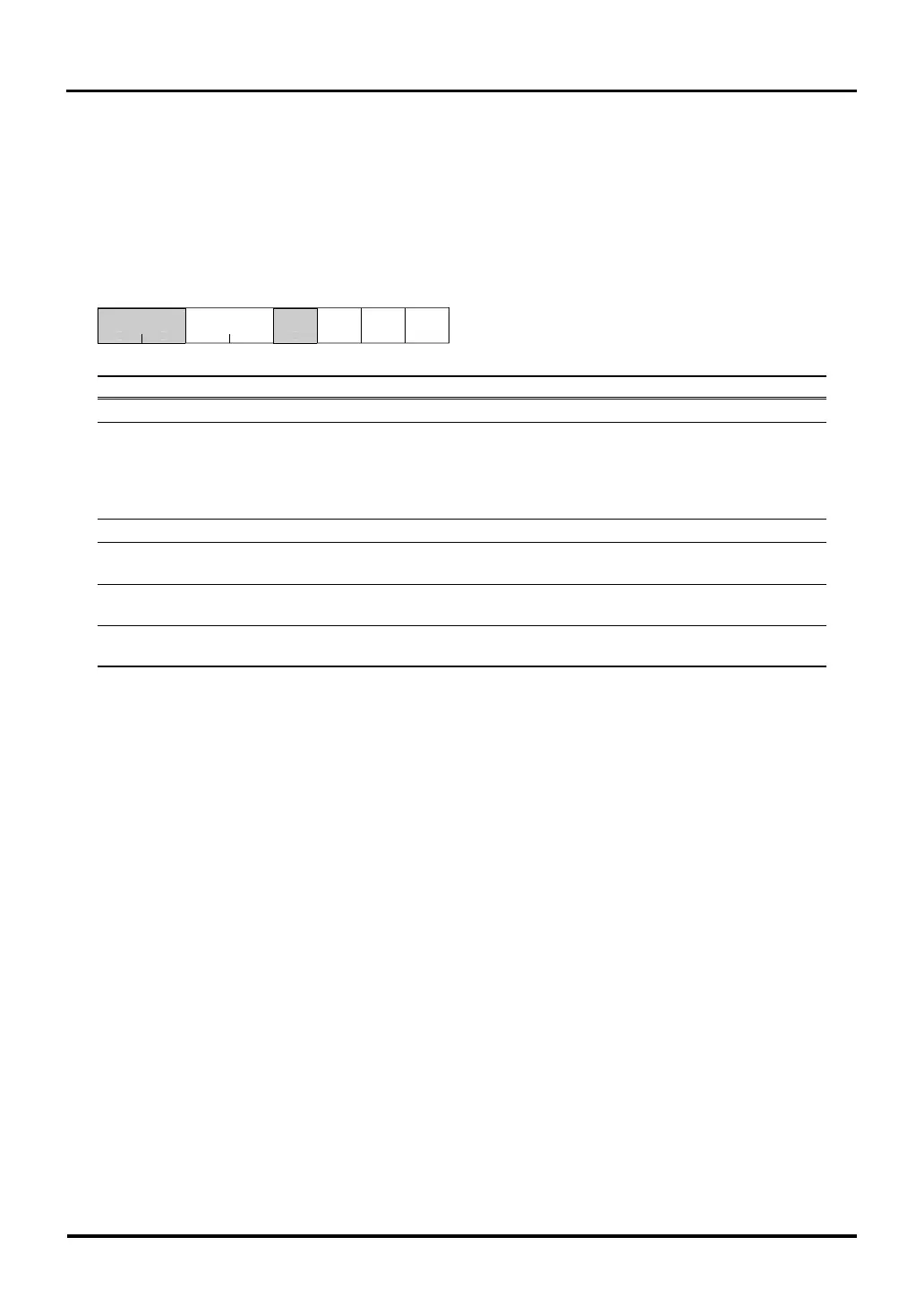

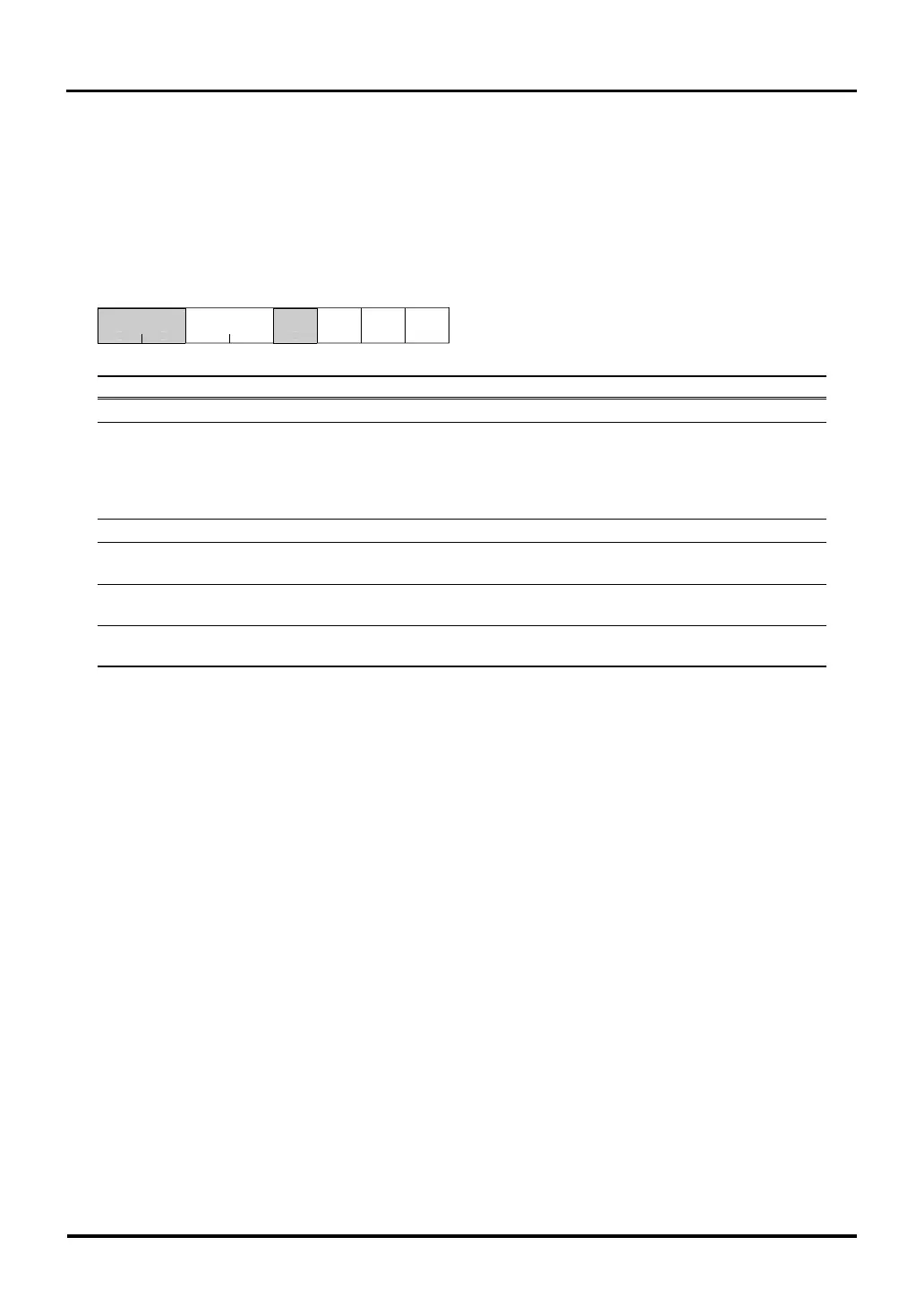

123456b7b0

TSTAT TBE TENCDIV

1010

<After reset: H’12>

b Bit Name Function R W

0, 1 No function assigned. Fix to "0". 00

2, 3 CDIV b2 b3 R W

BRG count source select bit 0 0: Select f(BCLK)

0 1: Select f(BCLK) divided by 8

1 0: Select f(BCLK) divided by 32

1 1: Select f(BCLK) divided by 256

4 No function assigned. Fix to "0". 00

5 TSTAT 0:Transmission stopped and no data in transmit buffer register R –

Transmit status bit 1:Transmitting now or data present in transmit buffer register

6 TBE 0:Data present in transmit buffer register R –

Transmit buffer empty bit 1: No data in transmit buffer register

7 TEN 0: Disable transmission R W

Transmit enable bit 1: Enable transmission

(1) CDIV (baud rate generator count source select) bits (Bits 2–3)

These bits select the count source for the Baud Rate Generator (BRG).

Note: • If f(BCLK) is selected as the count source for the BRG, care must be taken when setting the

BRG so that the baud rate will not exceed the maximum transfer speed. For details, see the

section in which the BRG register is explained.

(2) TSTAT (Transmit Status) bit (Bit 5)

[Set condition]

This bit is set to "1" by a write to the transmit buffer register while transmission is enabled.

[Clear condition]

This bit is cleared to "0" when transmission is idle (no data in the transmit shift register) and no data

exists in the transmit buffer register. This bit is also cleared by clearing the transmit enable bit.

(3) TBE (Transmit Buffer Empty) bit (Bit 6)

[Set condition]

This bit is set to "1" when data is transferred from the transmit buffer register to the transmit shift register

and the transmit buffer register is thereby emptied. This bit is also set by clearing the transmit enable bit.

[Clear condition]

This bit is cleared to "0" by writing data to the lower byte of the transmit buffer register while transmission

is enabled (TEN = "1").

(4) TEN (Transmit Enable) bit (Bit 7)

Transmission is enabled by setting this bit to "1" and disabled by clearing this bit to "0". If this bit is cleared to

"0" while transmitting data, the transmit operation stops.

Loading...

Loading...