12

12-55

Serial I/O

32180 Group User's Manual (Rev.1.0)

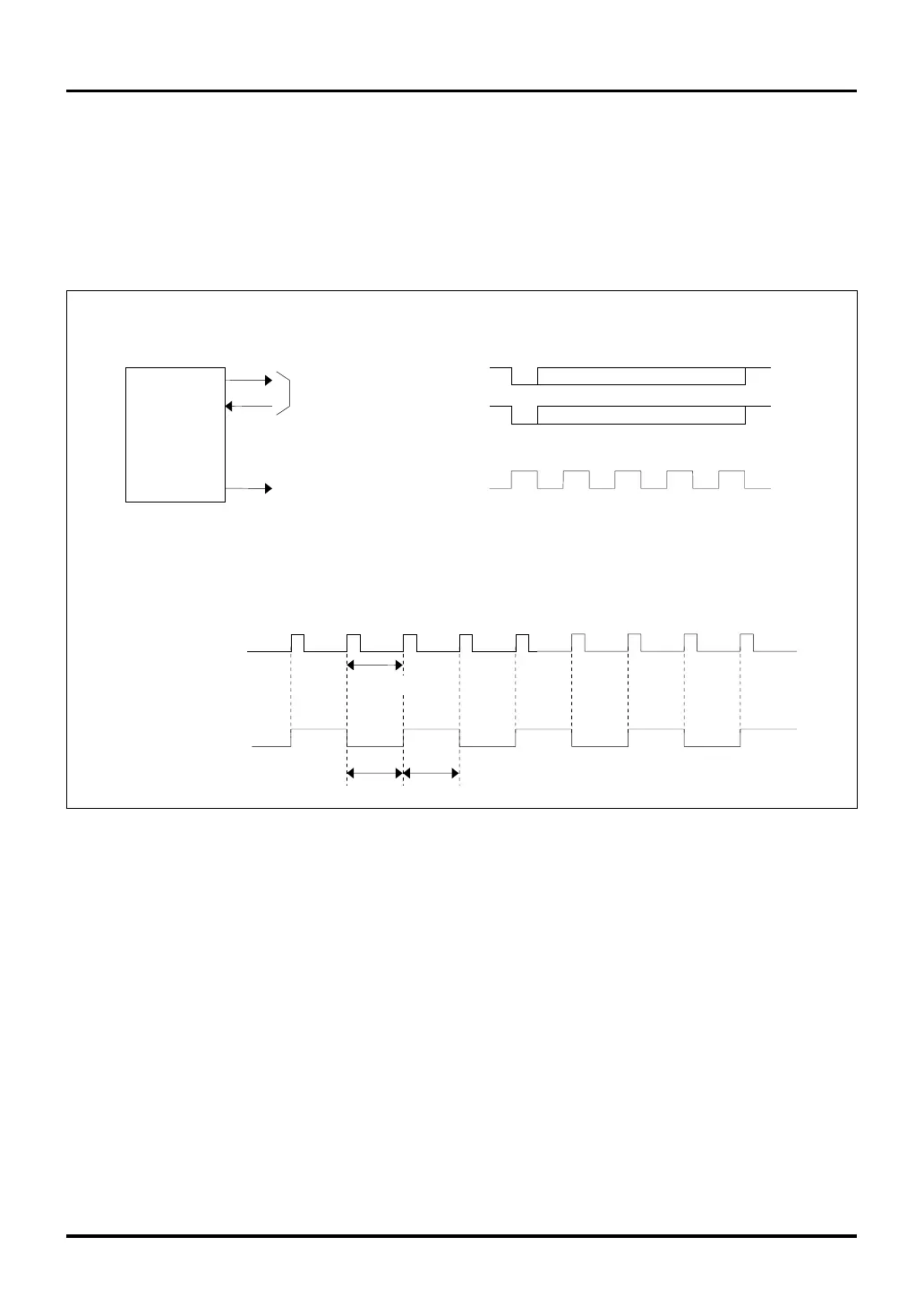

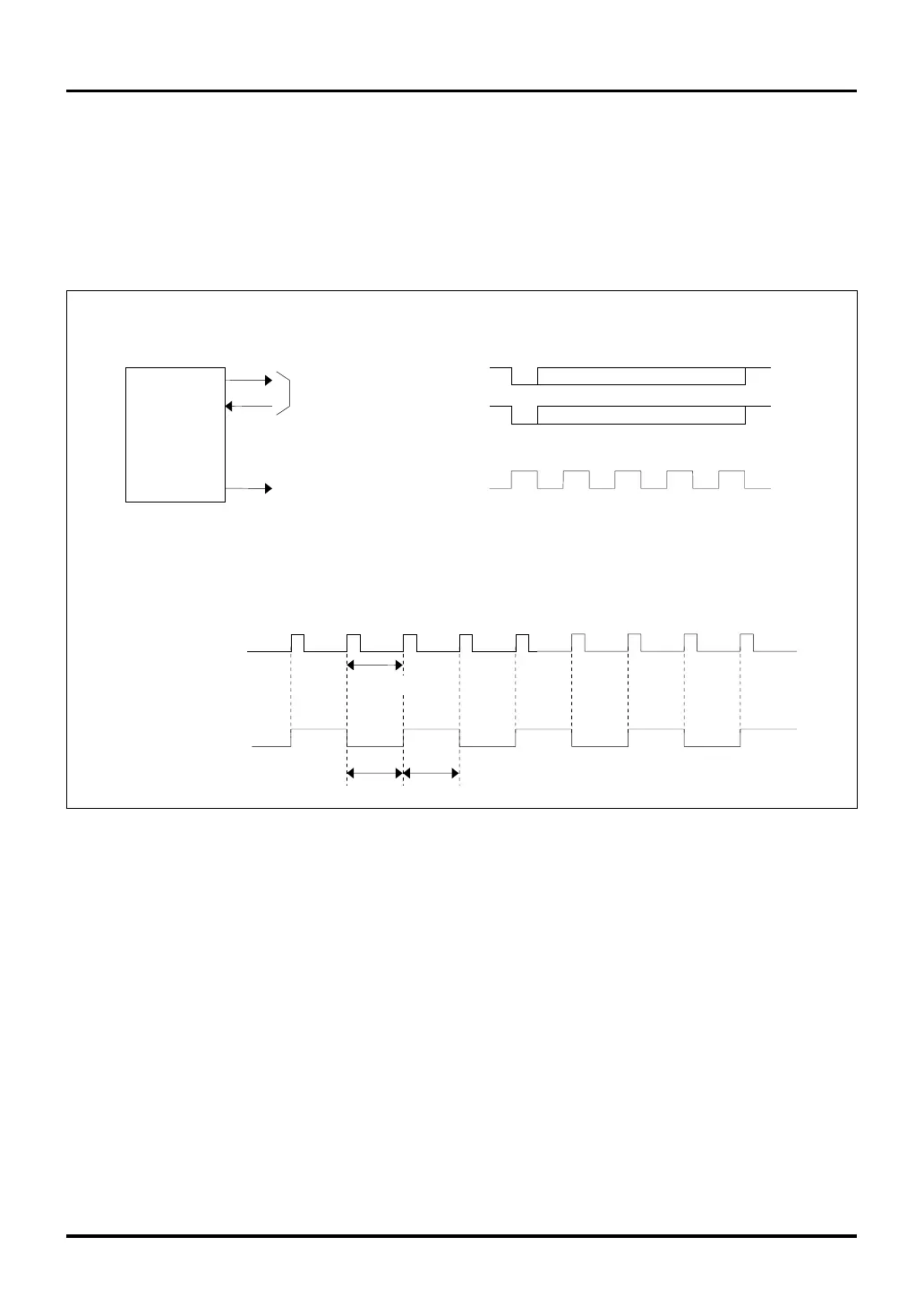

12.8 Fixed Period Clock Output Function

When using SIO0, SIO1, SIO4 or SIO5 in UART mode, the relevant port (P84, P87, P65 or P66) can be switched

for use as an SCLKO0, SCLKO1, SCLKO4 or SCLKO5 pin, respectively. That way, a BRG output clock divided by

2 can be output from the SCLKO pin.

Note: • This clock is output not just during data transfer.

12.8 Fixed Period Clock Output Function

Figure 12.8.1 Example of Fixed Period Clock Output

SCLKO

TXD

RXD

Clock output to

peripheral circuits

UART

transmission/reception

ST SP

Data

ST SPData

50%

50%

BRG period

Internal BRG

output

SCLKO output

1. Configuration when using BRG/2 clock

2. Operation timing

Loading...

Loading...