11

11-22

A-D Converters

32180 Group User's Manual (Rev.1.0)

11.2 A-D Converter Related Registers

11.2.4 A-D Scan Mode Registers 1

A-D0 Scan Mode Register 1 (AD0SCM1) <Address: H’0080 0085>

A-D1 Scan Mode Register 1 (AD1SCM1) <Address: H’0080 0A85>

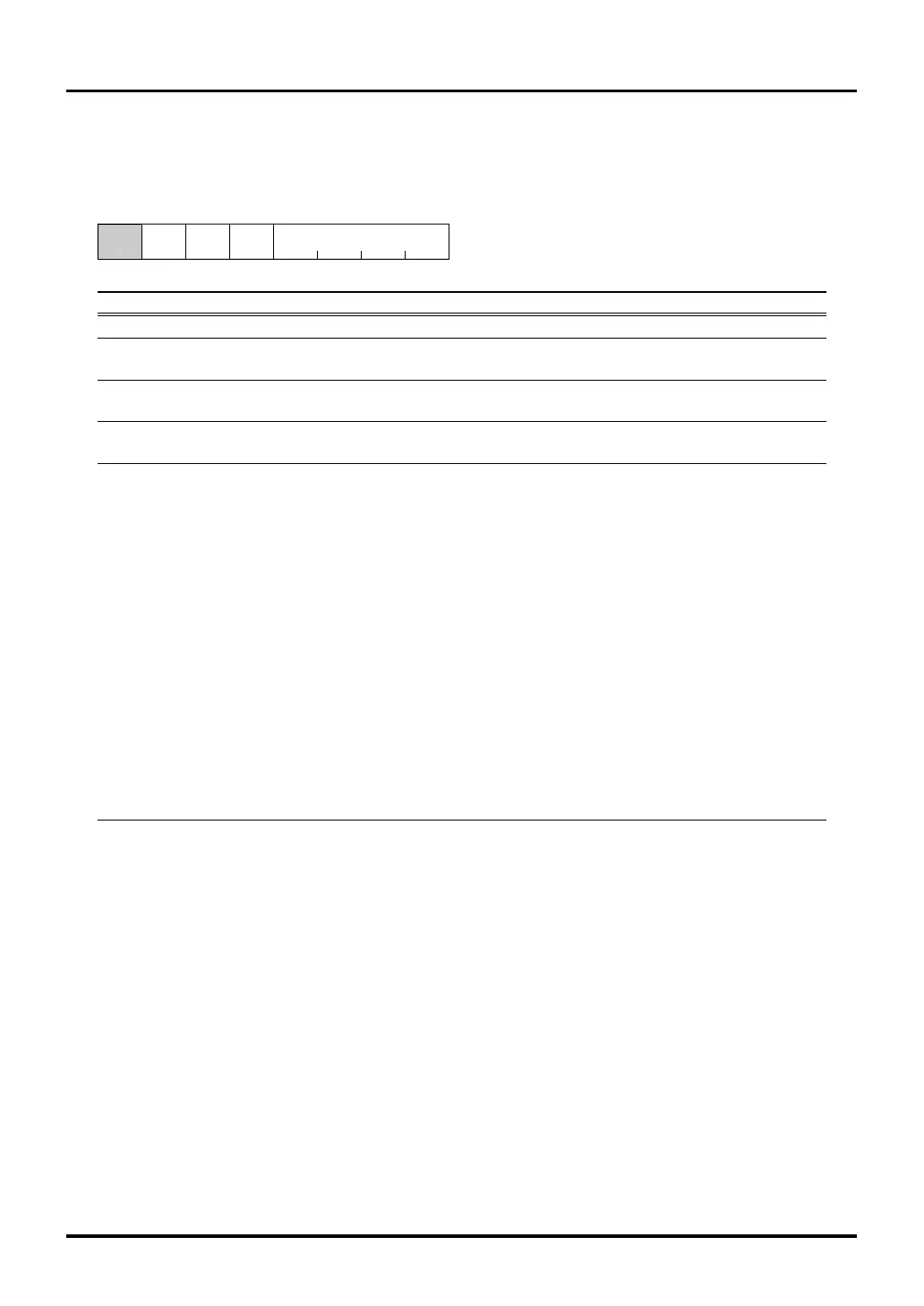

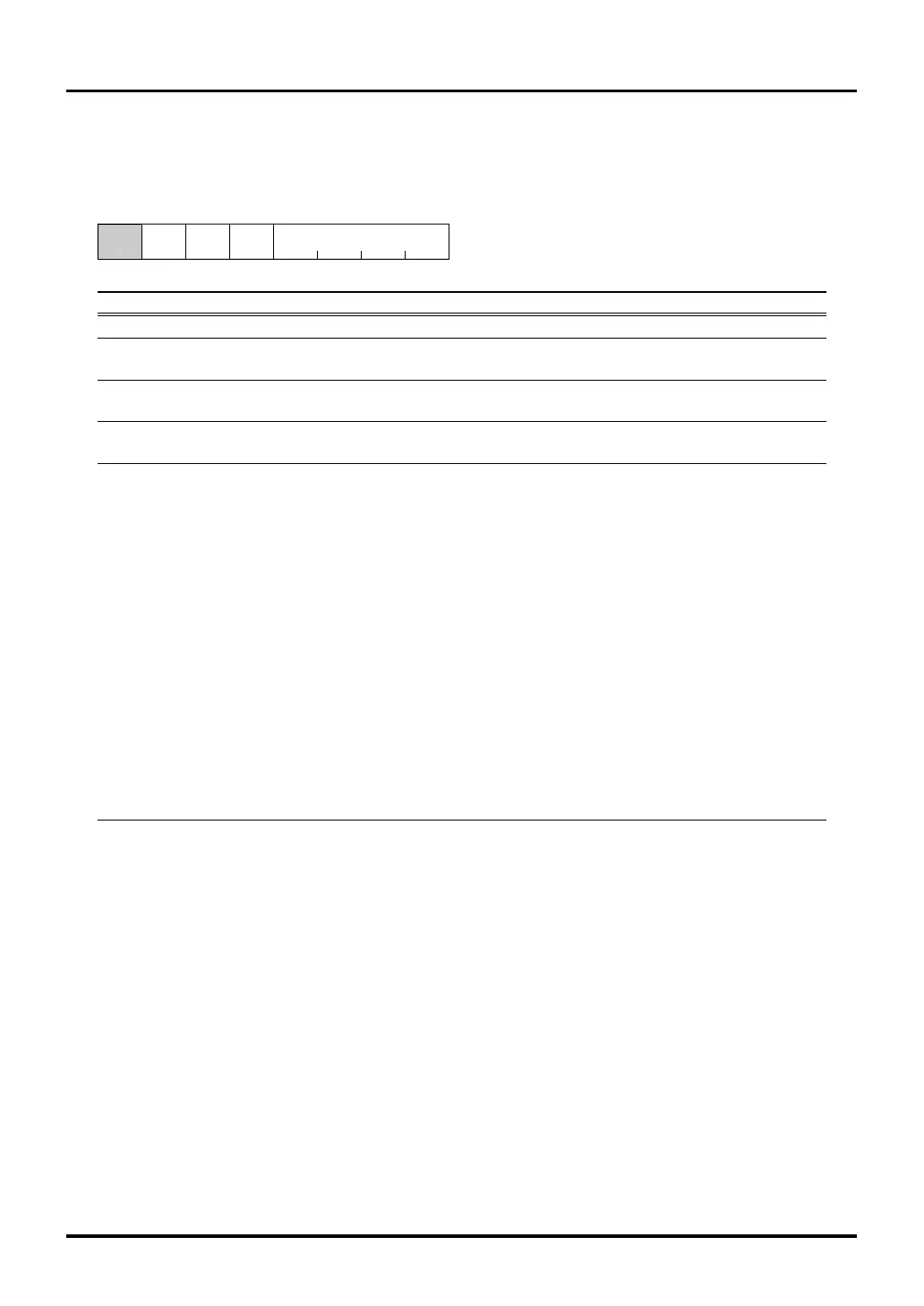

9 1011121314b15b8

ADCSPD ADCSHSL ADSCAN

0000000

ADCSHSPD

<After reset: H’00>

b Bit Name Function R W

8 No function assigned. Fix to "0". 00

9 ADCSPD (Note 1) 0: Normal speed R W

A-D conversion speed select bit 1: Double speed

10 ADCSHSL 0: Disable sample-and-hold R W

A-D conversion method select bit 1: Enable sample-and-hold

11 ADCSHSPD (Note 2) 0: Normal sample-and-hold R W

A-D sample-and-hold conversion speed select bit 1: Fast sample-and-hold

12–15 ADSCAN <For write> R W

A-D scan loop select bit ‘B0000–1111 (channels 0–15)

<For read during conversion> (i = 0, 1)

0000: Converting ADiIN0

0001: Converting ADiIN1

0010: Converting ADiIN2

0011: Converting ADiIN3

0100: Converting ADiIN4

0101: Converting ADiIN5

0110: Converting ADiIN6

0111: Converting ADiIN7

1000: Converting ADiIN8

1001: Converting ADiIN9

1010: Converting ADiIN10

1011: Converting ADiIN11

1100: Converting ADiIN12

1101: Converting ADiIN13

1110: Converting ADiIN14

1111: Converting ADiIN15

Note 1: The A-D conversion speed is determined by a combination of ADCSPD, ADCSHSL and ADCSHSPD bits and the A-D

Conversion Speed Control Register ADCVSD bit.

Note 2: Setting of this bit is effective when the sample-and-hold function is enabled by ADCSHSL bit.

A-D Scan Mode Registers 1 are used to select operation mode, conversion speed and scan loop when the A-D

Converter is operating in scan mode. The channels selected with the scan loop select bit are scanned sequen-

tially beginning with channel 0 (n-channel scan).

Loading...

Loading...