5

5-17

INTERRUPT CONTROLLER (ICU)

32180 Group User’s Manual (Rev.1.0)

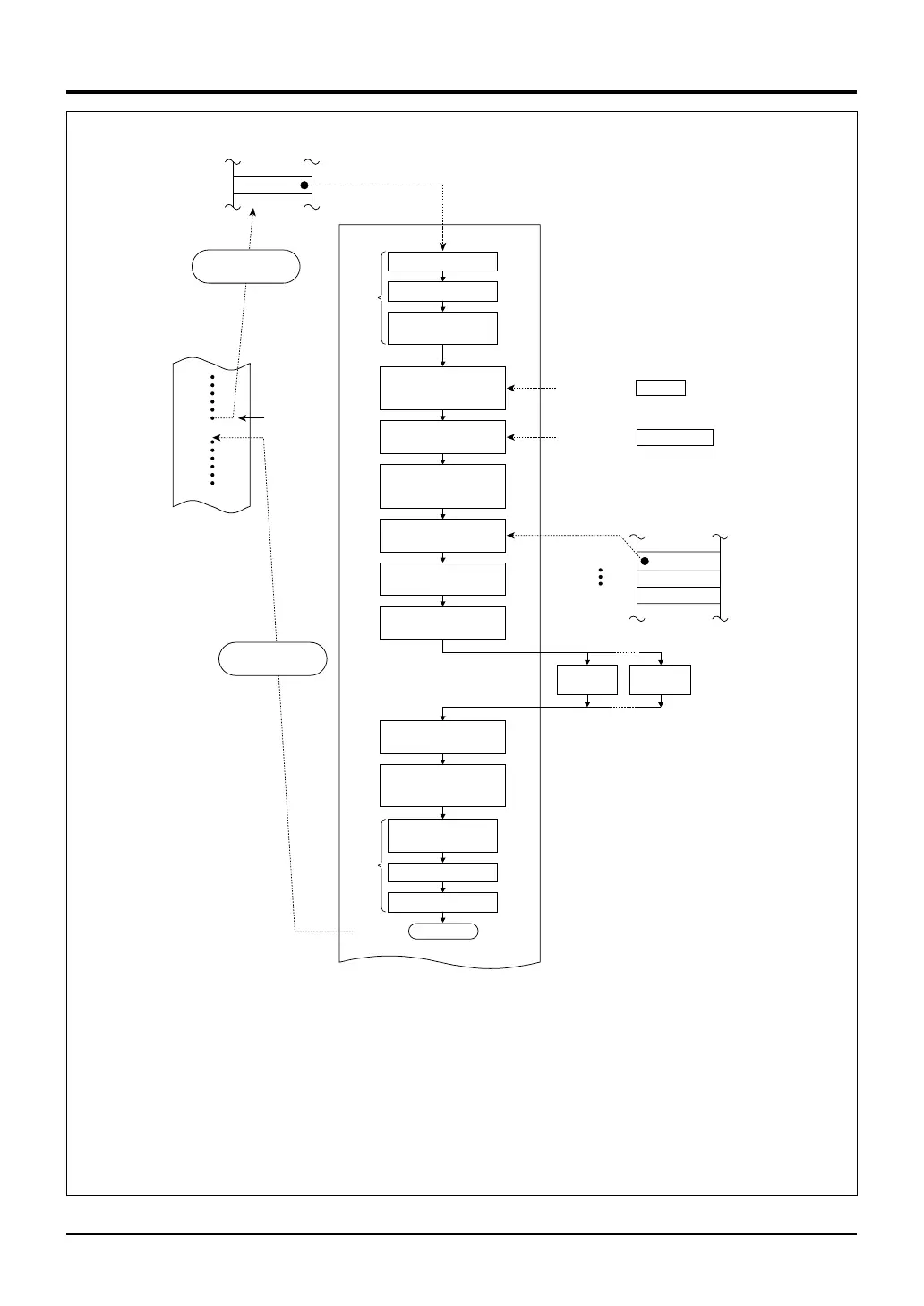

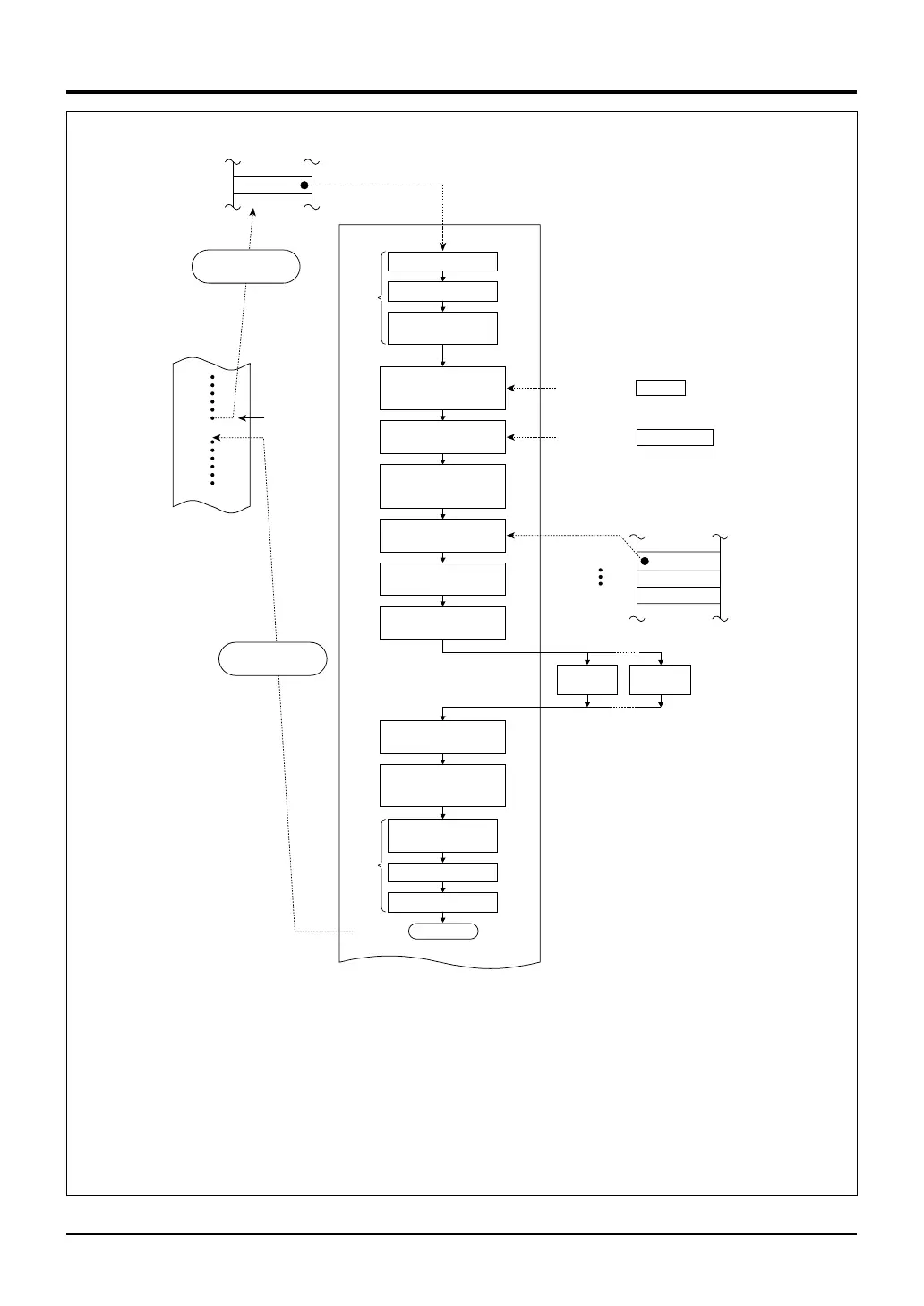

Figure 5.5.2 Typical Handler Operation for Interrupts from Internal Peripheral I/O

5.5 Description of Interrupt Operation

Note 1: For operations at EIT acceptance and return from EIT, also see Section 4.3, "EIT Processing Procedure."

Note 2: Do not read the Interrupt Vector Register (IVECT) or write to the Interrupt Request Mask Register (IMASK)

in the EIT handler unless interrupts are disabled (PSW register IE bit = 0).

Note 3: When multiple interrupts are disabled, execute processing in [4]. Processing in [4] is unnecessary if multiple

interrupts are enabled by executing processing in [6] and [9].

Note 4: To enable multiple interrupts, execute processing in [6] and [9].

Note 5: To reenable interrupts (by setting the IE bit to 1) after reading the Interrupt Vector Register (IVECT),

perform a dummy access to the internal memory, etc. before reenabling interrupts. In the example here,

there is no need to add a dummy access because the ICU vector table is read after reading the IVECT register.

Similarly, to reenable interrupts (by setting the IE bit to 1) after writing to the Interrupt Request Mask Register

(IMASK), perform a dummy access to the internal memory, etc. before reenabling interrupts.

H'0000 0080

BRA instruction

Read Interrupt Vector

Register (IVECT)

Read ICU vector table

Branch to the interrupt handler

for each internal peripheral I/O

RTE

H'0080 0004

H'0000 0094

H'0000 0113

Interrupt

handler

EI (External Interrupt)

handler

EI (External Interrupt)

vector entry

Interrupt handler

start address

Program being

executed

Interrupt

generated

IVECT

Save BPC to the stack

Save PSW to the stack

Save general-purpose

registers to the stack

Restore BPC from the stack

Restore PSW from the stack

Restore general-purpose

registers from the stack

Read and save Interrupt

Request Mask Register

(IMASK) to the stack

IMASK

H'0080 0000

Set PSW register IE bit to 1

Clear PSW register

IE bit to 0

Restore Interrupt Request

Mask Register (IMASK)

from the stack

[1]

[2]

[3]

[5]

[7]

[8]

[9]

[6]

[10]

[11]

ICU vector table

(Note 1)

(Note 1)

Hardware preprocessing

when EIT is accepted

Hardware postprocessing

when RTE instruction

is executed

Read and overwrite

Interrupt Request Mask

Register (IMASK)

[4]

[12]

(Note 2)

(Note 2)

(Note 3)

(Note 4)

(Note 5)

(Note 4)

(Note 2)

Interrupt

handler

[1] to [12]: Processing of EI

by interrupt handler

Loading...

Loading...