9

9-2

DMAC

32180 Group User’s Manual (Rev.1.0)

9.1 Outline of the DMAC

The microcomputer internally contains a 10-channel DMAC (Direction Memory Access Controller). It allows data

to be transferred at high speed between internal peripheral I/Os, between internal RAM and internal peripheral I/O,

or between internal RAMs, as initiated by a software trigger or requested from an internal peripheral I/O.

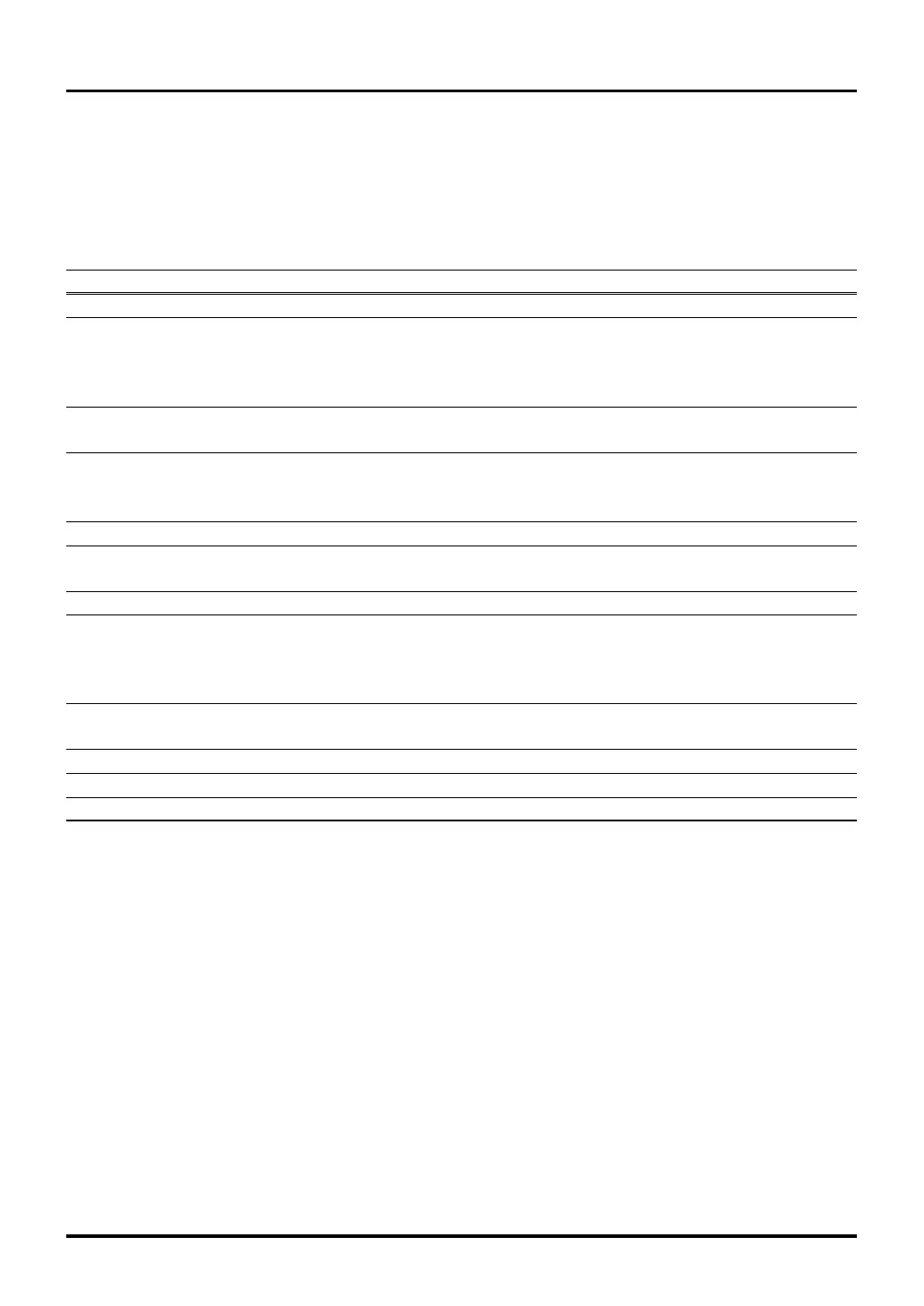

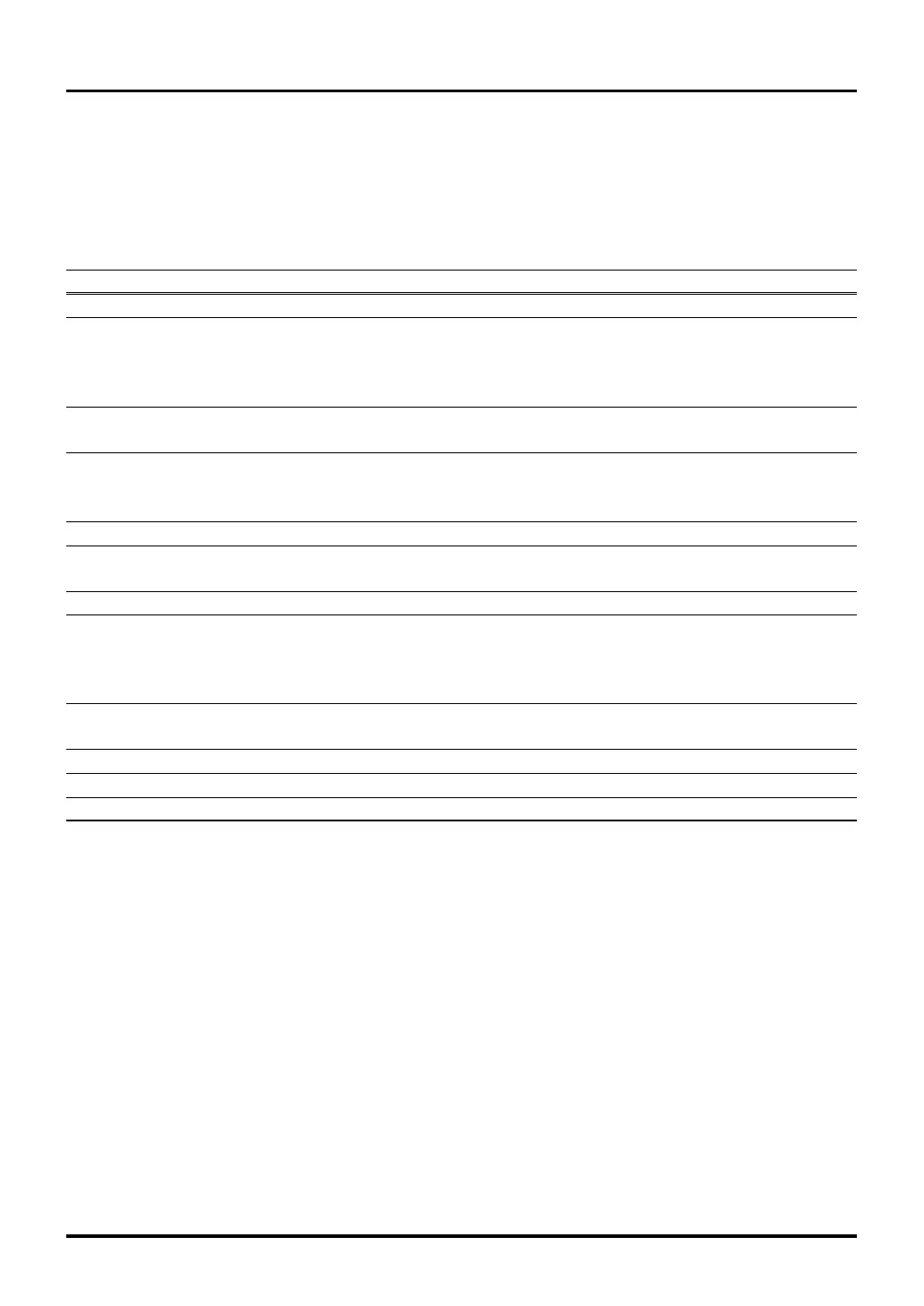

Table 9.1.1 Outline of the DMAC

Item Description

Number of channels 10 channels

Transfer request sources • Software trigger

• Request from internal peripheral I/Os: A-D converter, multijunction timer, serial I/O (reception

completed, transmit buffer empty) or CAN

• DMA channels can be cascaded (Note 1)

Maximum number of 65,536 times

times transferred

Transferable address • 64 Kbytes (address space from H’0080 0000 to H’0080 FFFF)

space • Transfers between internal peripheral I/Os, between internal RAM and internal peripheral I/O, and

between internal RAMs are supported.

Transfer data size 16 or 8 bits

Transfer method Single transfer DMA (control of the internal bus is relinquished for each transfer performed), dual-

address transfer

Transfer mode Single transfer mode

Direction of transfer One of three modes can be selected for the source and destination:

• Address fixed

• Address incremental

• Ring buffered

Channel priority DMA0 > DMA1 > DMA2 > DMA3 > DMA4 > DMA5 > DMA6 > DMA7 > DMA8 > DMA9

(Priority is fixed)

Maximum transfer rate 13.3 Mbytes per second (when internal peripheral clock BCLK = 20 MHz)

Interrupt request Group interrupt request can be generated when each transfer count register underflows.

Transfer area 64 Kbytes from H’0080 0000 to H’0080 FFFF (Transferable in the entire RAM/SFR area)

Note 1: The DMA channels can be cascaded in the manner described below.

• Start DMA transfer on DMA1 upon completion of one DMA transfer on DMA0

• Start DMA transfer on DMA5 upon completion of all DMA transfers on DMA0 (upon underflow of the transfer count

register)

• Start DMA transfer on DMA2 upon completion of one DMA transfer on DMA1

• Start DMA transfer on DMA0 upon completion of one DMA transfer on DMA2

• Start DMA transfer on DMA3 upon completion of one DMA transfer on DMA2

• Start DMA transfer on DMA4 upon completion of one DMA transfer on DMA3

• Start DMA transfer on DMA6 upon completion of one DMA transfer on DMA5

• Start DMA transfer on DMA7 upon completion of one DMA transfer on DMA6

• Start DMA transfer on DMA5 upon completion of one DMA transfer on DMA7

• Start DMA transfer on DMA8 upon completion of one DMA transfer on DMA7

• Start DMA transfer on DMA9 upon completion of one DMA transfer on DMA8

9.1 Outline of the DMAC

Loading...

Loading...